计算机组成原理

本文最后更新于:2023年2月28日 下午

[toc]

LC-3基本原理

基本概念

1)名词

| 英语 | 中文 | 释义 |

|---|---|---|

| Instruction Set Architecture | 指令集架构 | specifies the set of instructions the computer can perform |

| data types, addressing mode | ||

| Microarchitecture | 微架构 | detailed organization of a processor implementation |

| different implementations of a single ISA | ||

| Circuits | 电路 | combine basic operations to realize microarchitecture |

| many different ways to implement a single function (e.g., addition) | ||

| Assembly language | 汇编语言 |

2)知识点

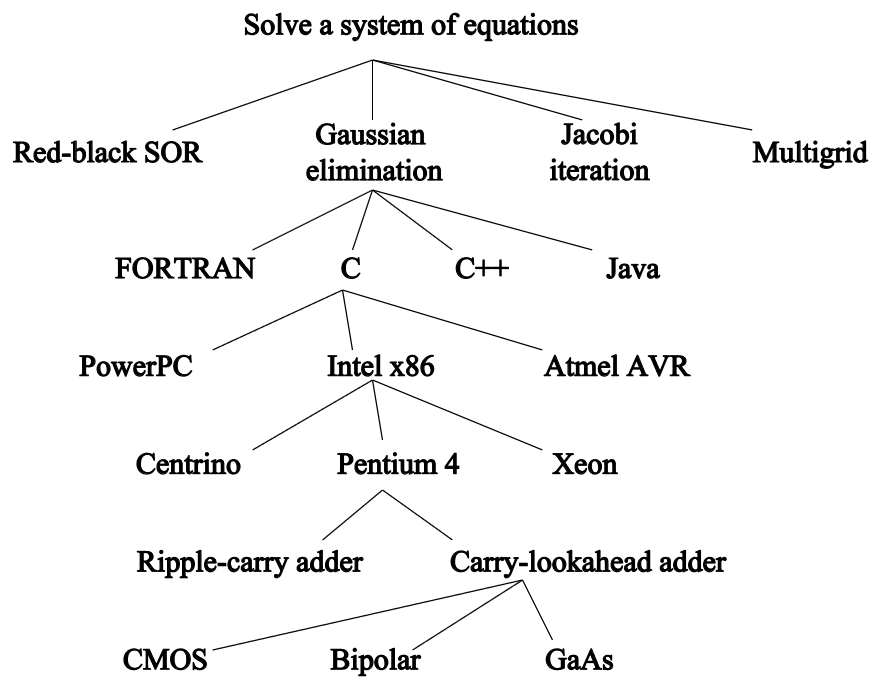

转换层次

Layers of a Computer System and Its Transformation

graph TB;

1[Problem] --Software Design---> 2[Algorithm]

2 --Programming---> 3[Program];

3 --Compiling/Interpreting---> 4[Instruction Set Architecture/ISA];

4 --Processor Design---> 5[Microarchitecture];

5 --Logic/Circuit Design---> 6[Circuit];

6 --Process Engineering/Fabrication---> 7[Devices]

Many Choices at Each Level

运算与转换

1)名词

| 英文 | 中文 | 释义 |

|---|---|---|

| analog number | 模拟信号 | |

| digital number | 数字信号 | |

| binary digit(bit) | 位 | 信息的基本单位 |

| Non-positional notation/Weighted positional notation | 非位置数字/权重位置数字 | |

| unsigned integer/signed Integers | 无符号整数/有符号整数 | |

| sign-magnitude/set MS bit | 符号值/符号位 | 二进制数中的第一位0/1 |

| sign-and-magnitude | 原码 | |

| 1’s Complement | 1的补码/反码 | |

| 2’s Complement | 2的补码/补码 | |

| overflow | 溢出 | |

| Binary | 二进制 | |

| Decimal | 十进制 | |

| Hexdecimal | 十六进制 | 前缀0x |

| arithmetic circuits | 运算电路 | |

| Binary | 二进制 | |

| Decimal | 十进制 | |

| Single-precision IEEE floating point number | IEEE标准单精度浮点数 |

2)知识点

考点总结

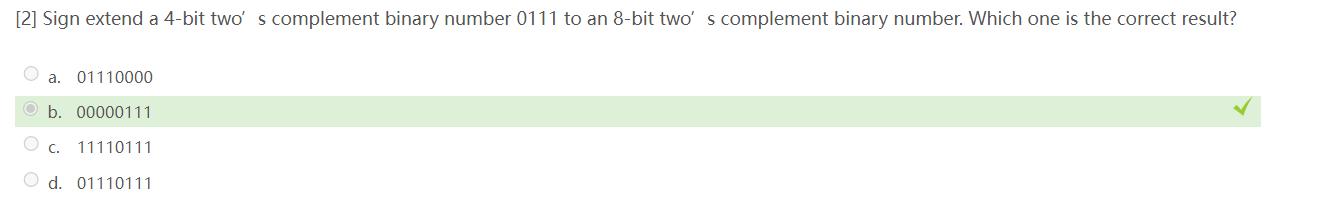

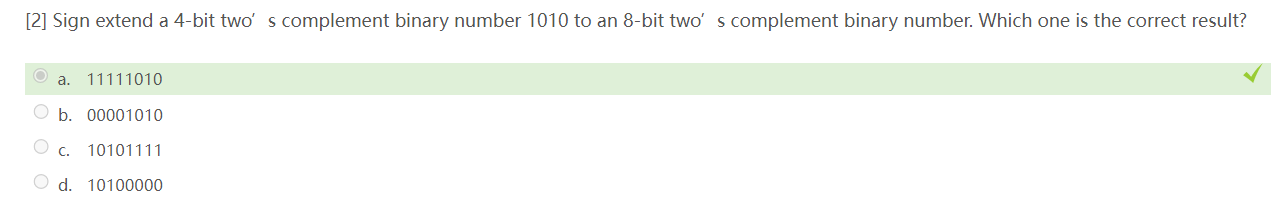

- 码间转换

- 无符号数与反码/补码转换(进制转换)

- 有符号数与反码/补码转换(保留符号取反+1)

- 不同位数补码转换(4位<->8位)

- 溢出判断(进制求和相同)

- IEEE浮点数计算(位数意义/计算公式)

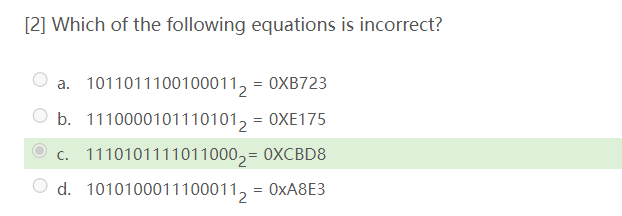

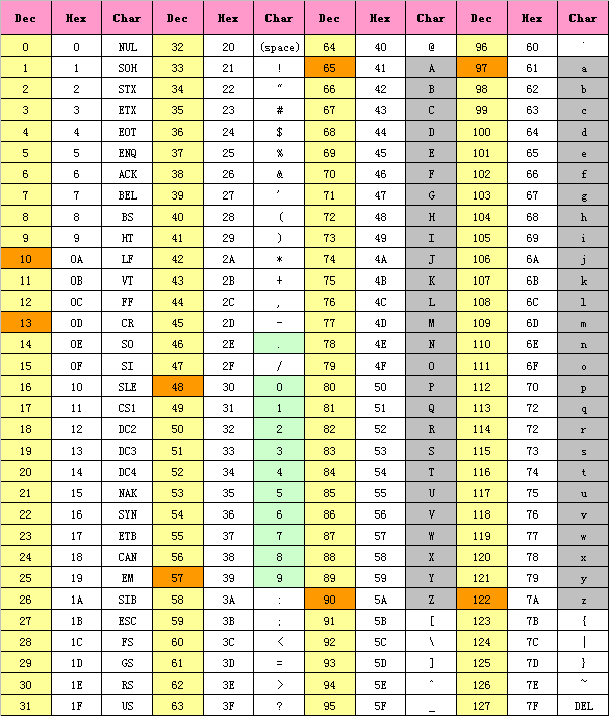

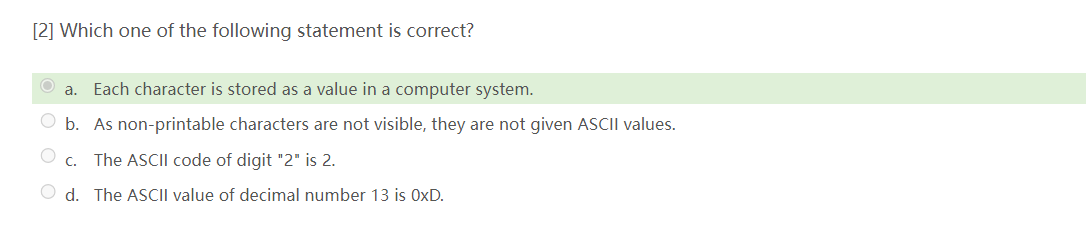

- ASCII理解判断

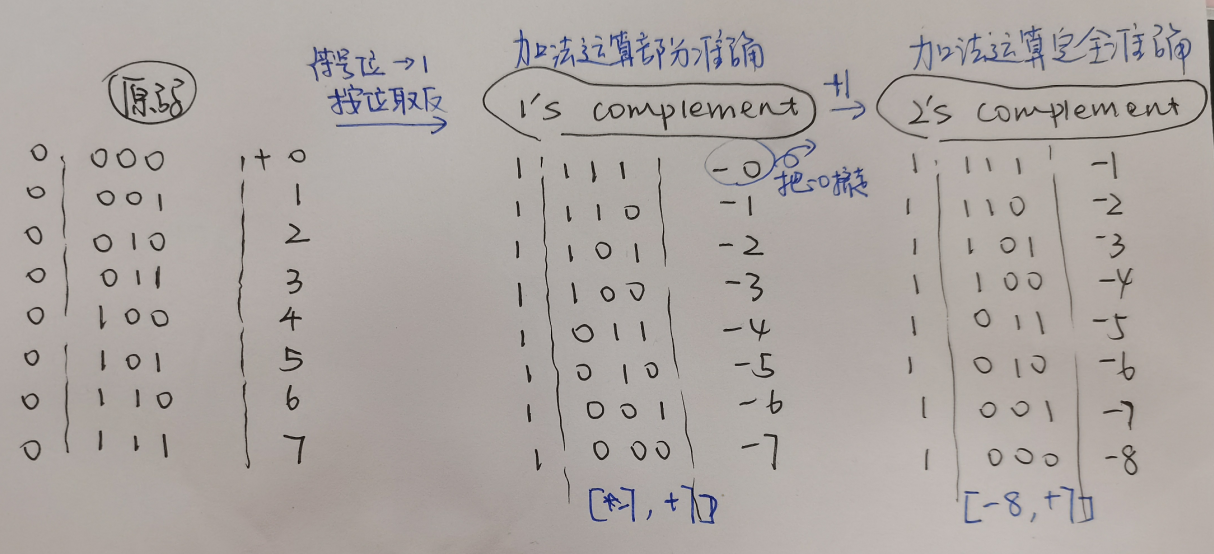

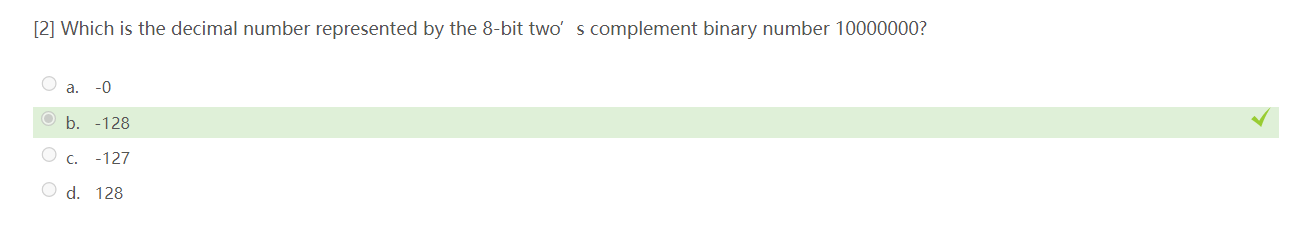

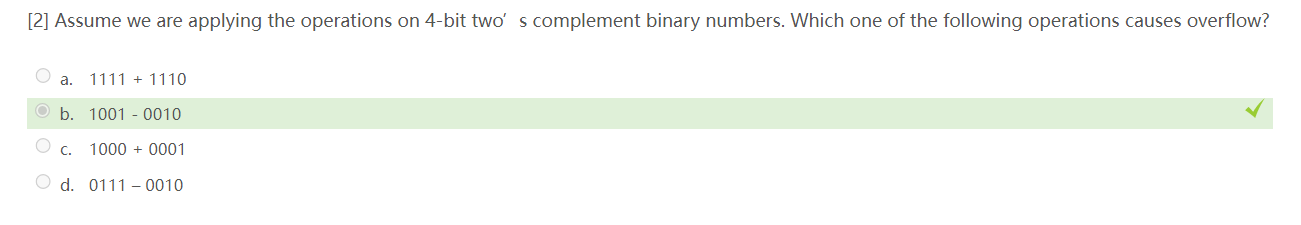

反码/补码/溢出

原码->反码->补码

-

怎么求

-

出现原因

graph LR; 0[sign-magnitude] --符号值加法结果不准确--> 1[1's Complement] --+-0/符号值加法结果部分准确--> 2[2's Complement]

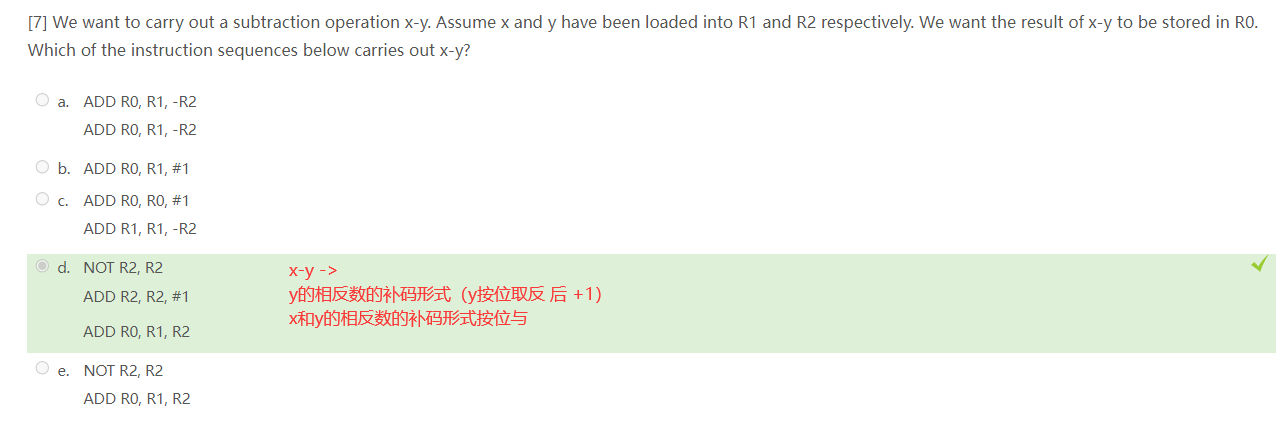

– 作业 –

溢出

补码的二进制运算结果 与 其十进制不一致

–作业–

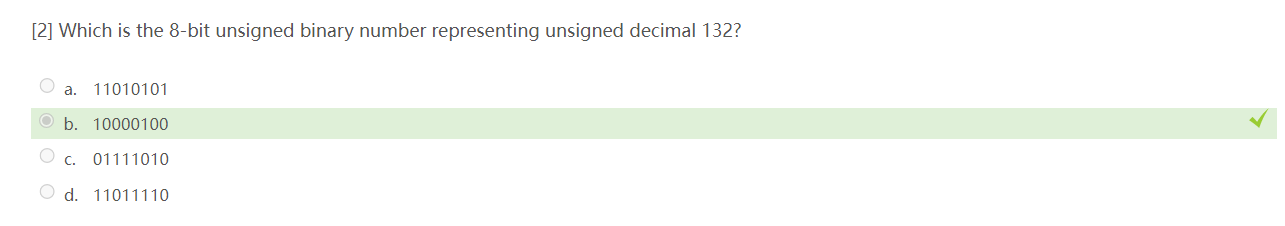

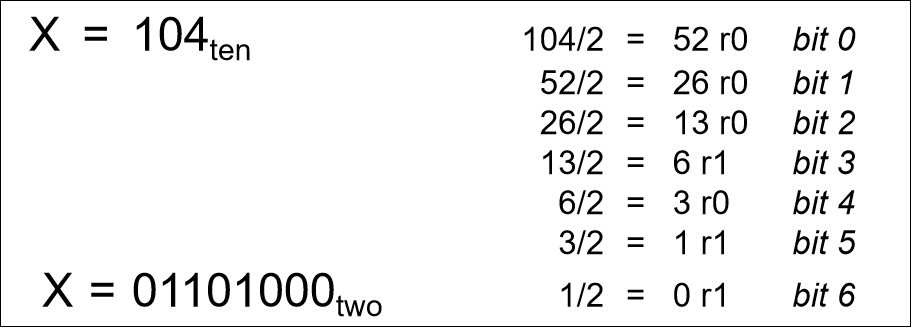

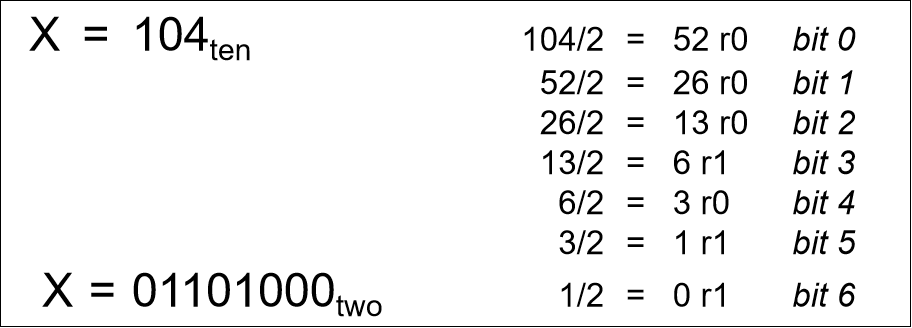

进制转换

- 它进制 -> 十进制:权重加和(整数/小数)

- 十进制 -> 它进制:

- 辗转相除取余数(整数)/(辗转相乘取整数部分(小数))

- 减幂

- 辗转相除取余数(整数)/(辗转相乘取整数部分(小数))

–作业–

ASCII码

对译表

–作业–

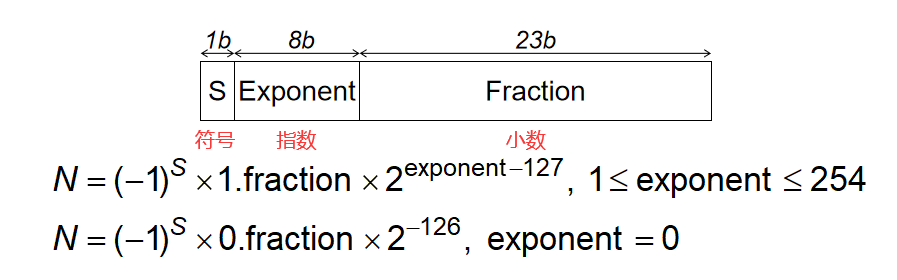

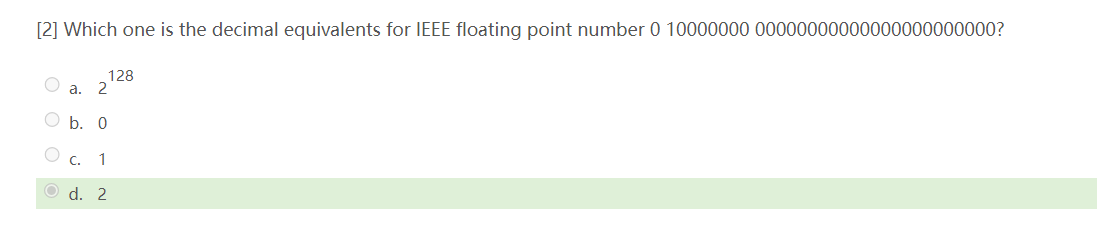

IEEE浮点数

-

IEEE单精度浮点数

-

指数 (整数Bin) --> (Dec)

-

小数 (小数Bin) --> (Dec)

1+小数/0+小数

-

–作业–

数字逻辑

1)名词

| 英文 | 中文 | 释义 |

|---|---|---|

| metal-oxide semiconductor (MOS) | 金属氧化物半导体 | |

| Complementary Metal-Oxide Semiconductor (CMOS) | 互补金属氧化物半导体 | 同时含有n/p型MOS的电路 |

| Gate | 栅极 | |

| Source | 源极 | #1 |

| Drain | 漏极 | #2 |

| Logic Gate | 逻辑门 | |

| Inverter | 反相器,非门 | |

| Combinational Logic Circuit | 组合逻辑电路 | |

| Decoder | 译码器 | |

| Multiplexer (MUX) | 多路复用器 | |

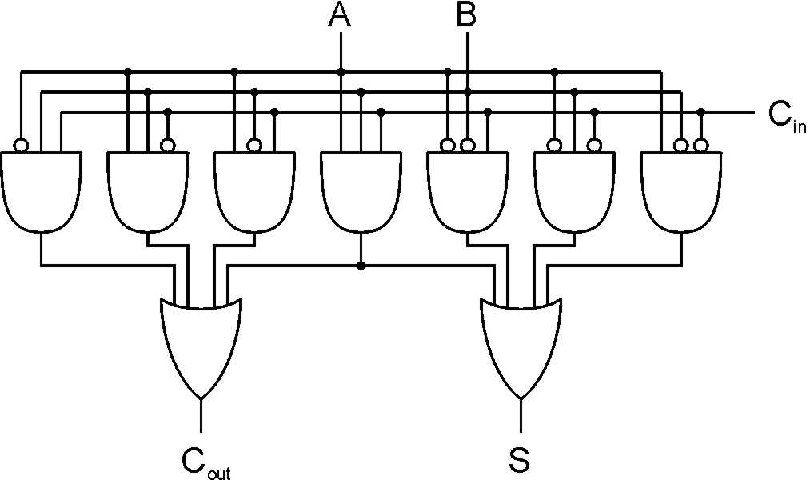

| Full Adder | 全加器 | |

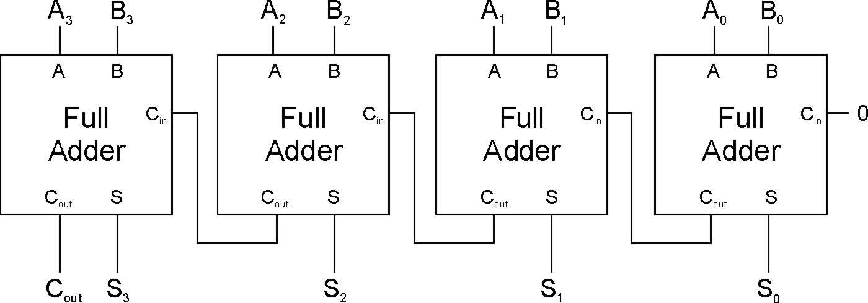

| Four-bit Adder | 4位加法器 | |

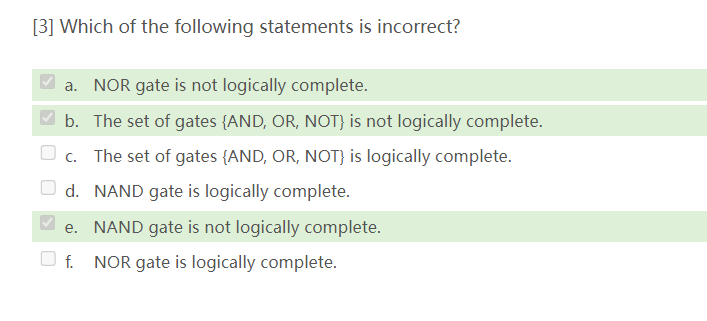

| Logical Completeness | 逻辑完备性 | |

| carry-in | 进位输入 | |

| carry-out | 进位输出 | |

| Storage Element | 存储单元 | |

| Sequential Logi Circuit | 时序逻辑电路 | |

| Latch/Trigger/Register | 锁存器/触发器/寄存器 | latch强调的是它的工作特性 trigger强调的是工作机制( 如沿触发或电平触发等) register则是它在计算机组成中的作用 |

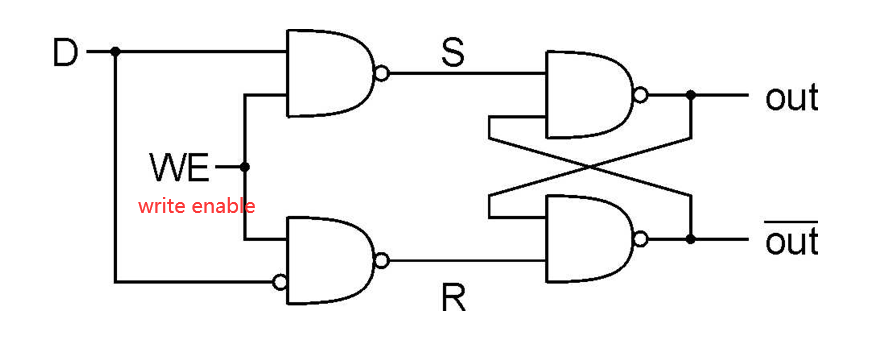

| R-S Latch | RS锁存器 | |

| quiescent | 静态 | RS均为1,维持原态 |

| set | 置 | |

| Gated D-Latch | 门控D锁存器‘ | |

| Address Space | 寻址空间 | |

| Address ability | 寻址能力 | |

| Memory | 内存 | |

| state | 状态 | The state of a system is a snapshot of all the relevant elements of the system at the moment the snapshot is taken. |

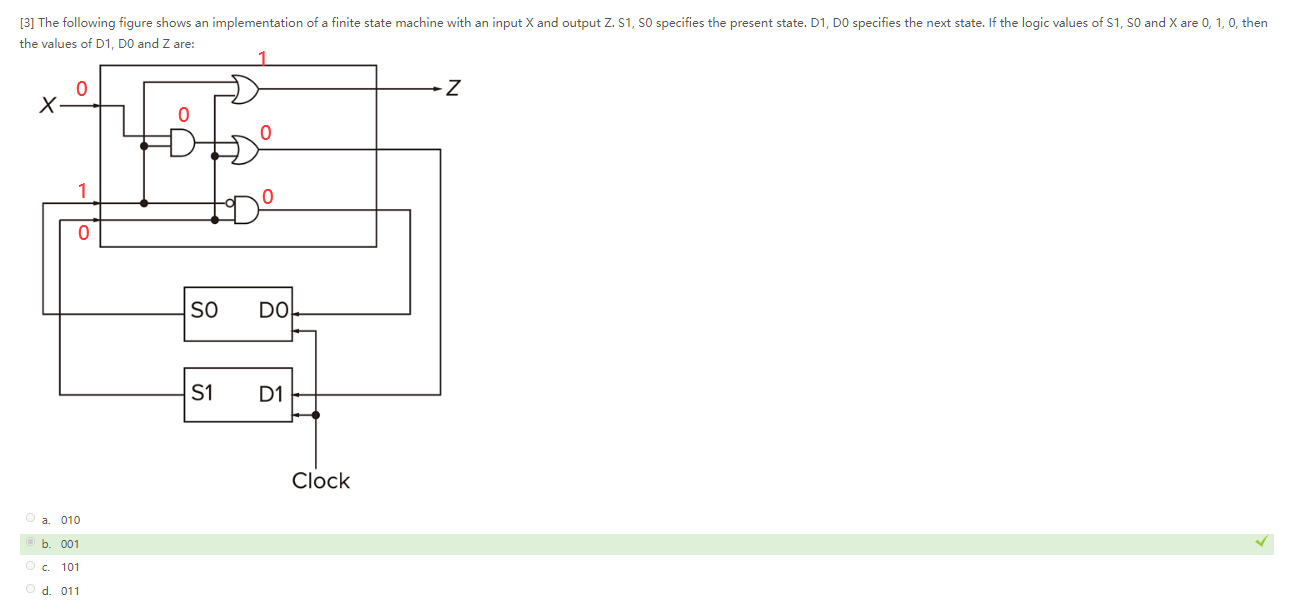

| Finite State Machine (FSM) | 有限状态机 | |

| Master-slave flipflop | 主从触发器 |

2)知识点

考点总结

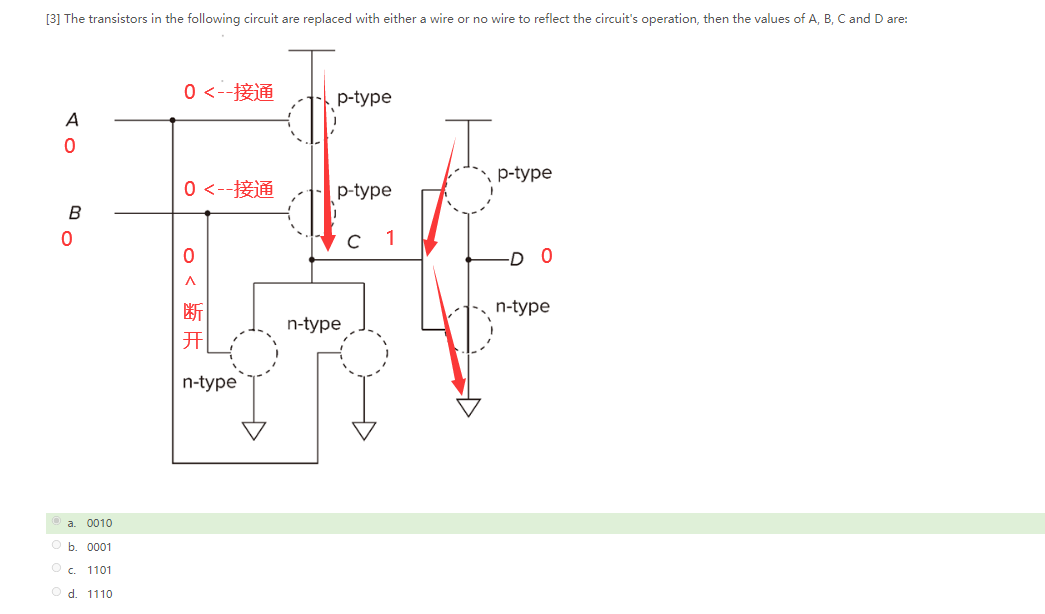

- p/n型MOS晶体管电路逻辑

- 逻辑完备性概念

- 门控D锁存器的工作逻辑

- 内存的动态判断

- 寻址能力/地址宽度/寻址空间概念理解

- 有限状态机的概念及特点

- 时序逻辑电路的工作逻辑

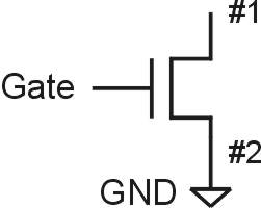

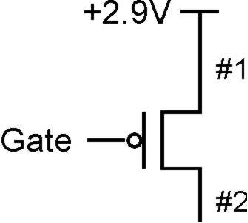

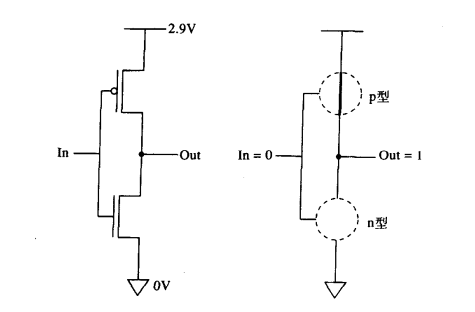

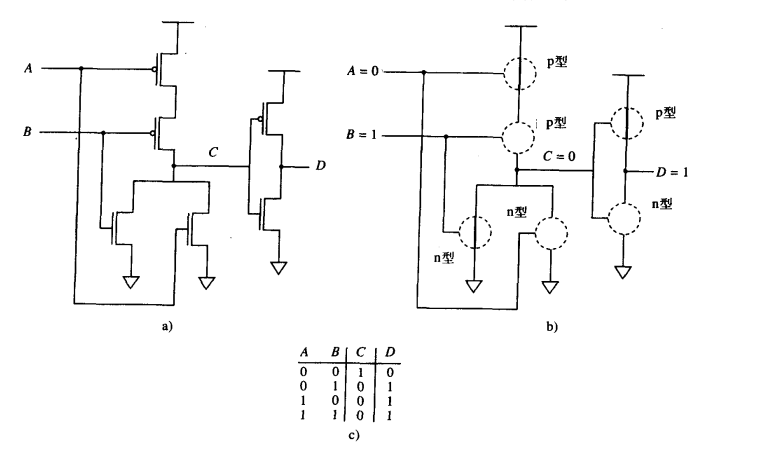

MOS晶体管

| MOS type | Theorem | Structure |

|---|---|---|

| n型MOS | 栅极+2.9V --> 1 栅极0 --> 0 |

|

| p型MOS | 栅极+2.9V --> 0 栅极0 --> 1 |

|

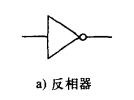

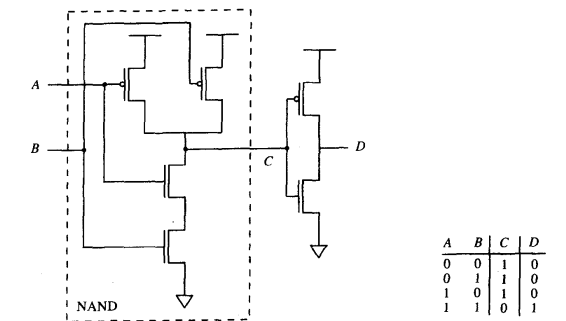

逻辑门

| Gate | Circuit | Note | Symbol | Re |

|---|---|---|---|---|

| 非门/反相器 |  |

NOT |  |

|

| 或非门 |  |

NOR |  |

|

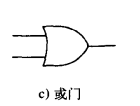

| 或门 |  |

OR |  |

或非门 + 反相器 |

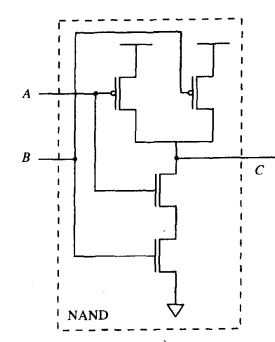

| 与非门 |  |

NAND |  |

|

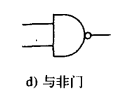

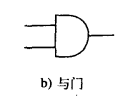

| 与门 |  |

AND |  |

与非门+反相器 |

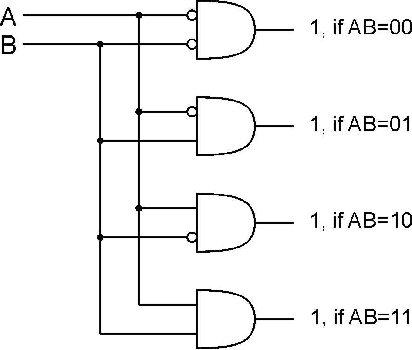

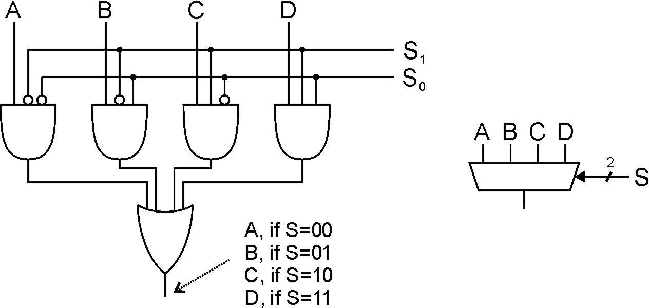

组合逻辑电路

| Type | Circuit | Func |

|---|---|---|

| 译码器 |  |

|

| 多路复用器 |  |

有选择信号Si决定被选择的输入输出 |

| 全加器 |  |

作两位数与进位输入的加法运算输出加和与进位输出 |

| 4位全加器 |  |

由4个全加器组成,计算4位数加法 |

–作业–

逻辑完备性

-

通过不同数量的与或非门就能实现其真值表

1

Can implement ANY truth table with AND, OR, NOT. -

与或非逻辑门的集合

1

The set og hates {AND,OR,NOT}.

–作业–

存储单元

graph LR;

1[R-S锁存器] --控制电路---> 2[门控D锁存器];

2 --多个---> 3[寄存器];

3 --多个+寻址能力---> 4[内存]

-

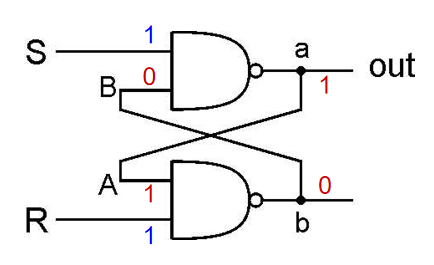

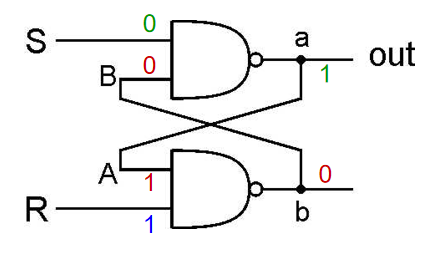

R-S锁存器

R-S四种状态 图示 功能 静态

保持置0的状态不变 静态

保持置1的状态不变 置0/清除

1.置R=0使状态置0

2.再置R=1记忆当前状态置1

1.置S=0使状态置0

2.再置S=1记忆当前状态 -

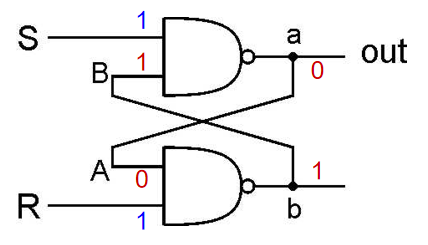

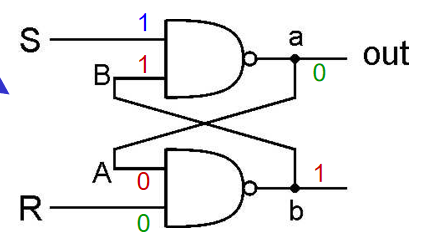

门控D锁存器

-

R-S锁存器 + 控制电路

WE = 1:

- 输入端 D = 0 --> R = 0 置0

- 输入端 D = 0 --> S = 0 置1

WE = 0:

输入端D无效,R/S为1,存储被记忆状态

-

-

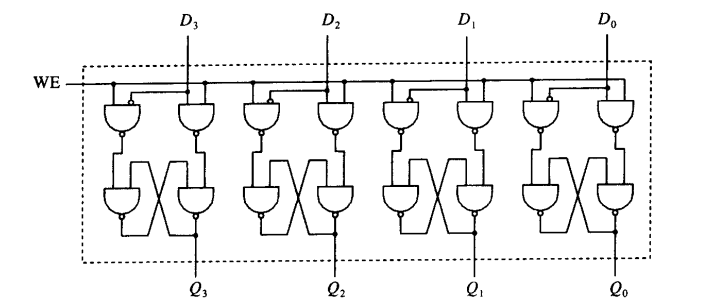

寄存器

将多个宽度为1-bit的锁存器组成指定宽度的独立单元,由同一控制信号控制

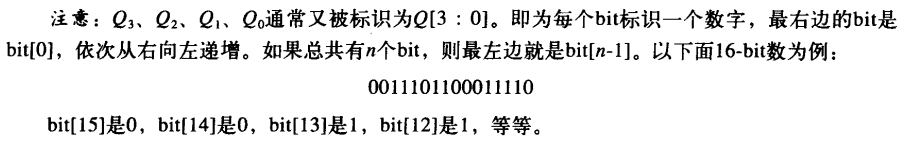

寄存器存储编号

可 从右至左/从左至右,保持一致即可,首索引为0.

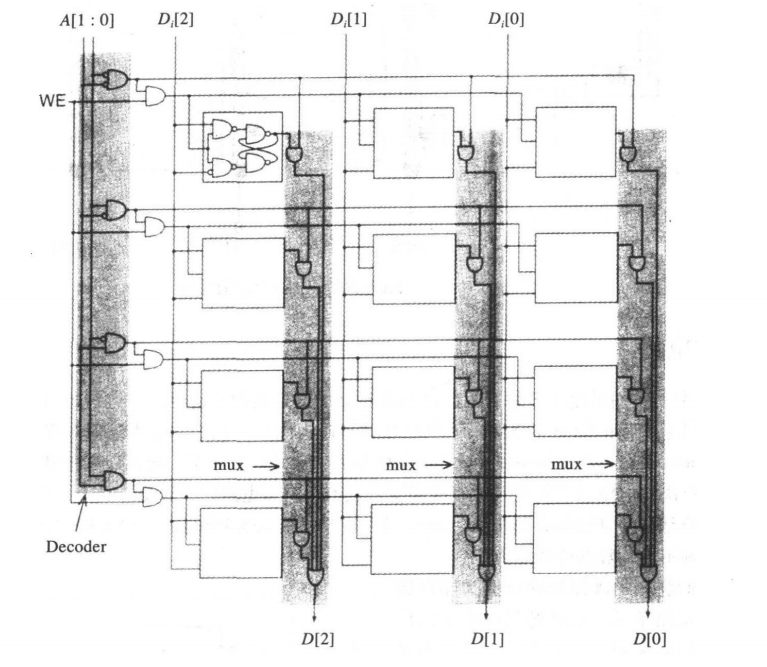

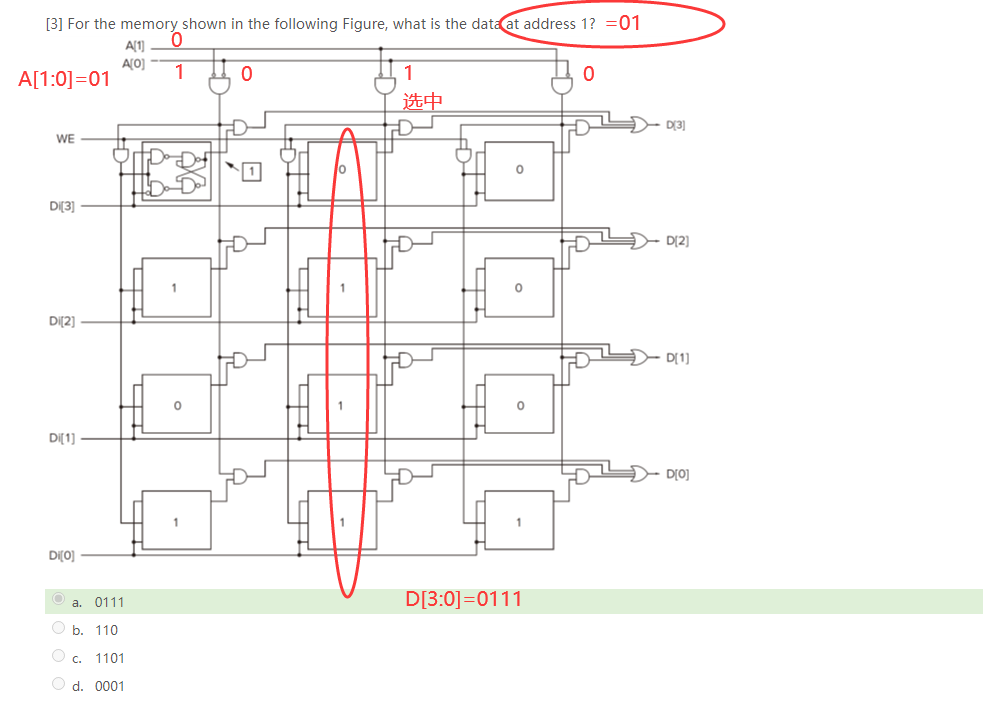

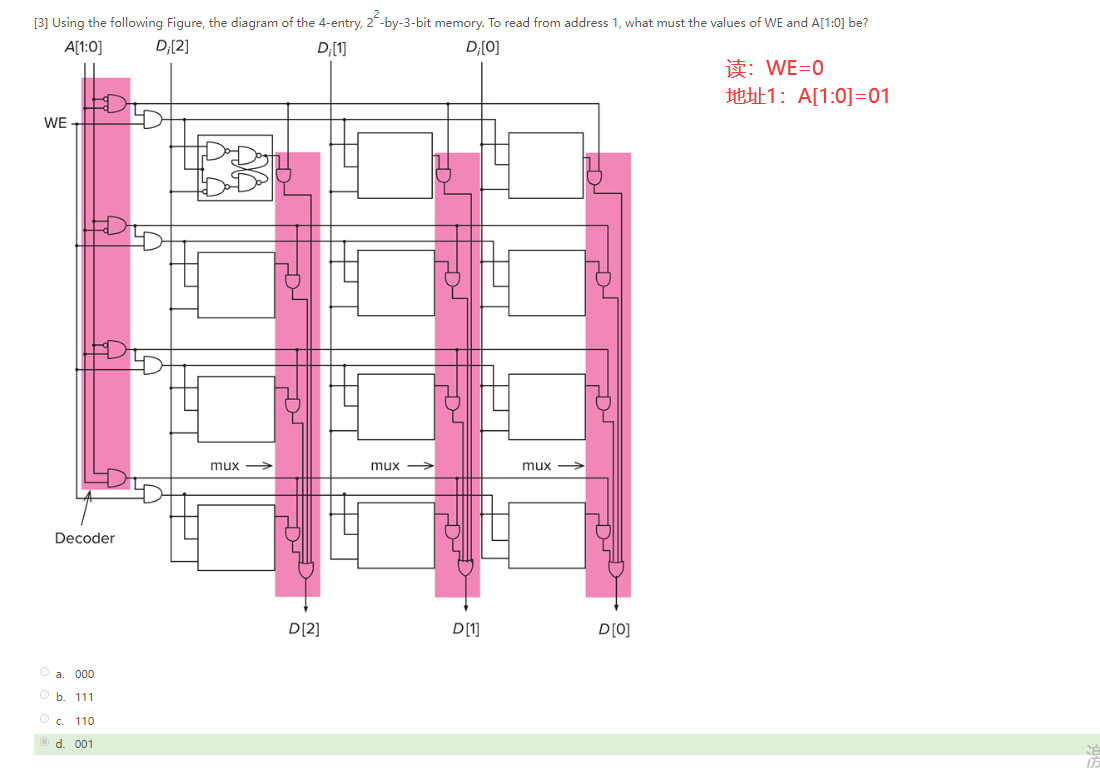

内存

-

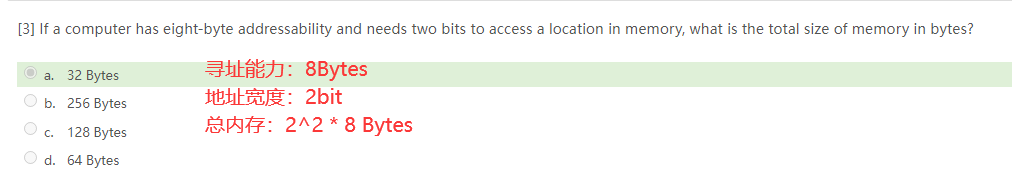

寻址空间

内存中可独立识别的存储位置总数为 寻址空间,如 16MB内存,包含约1600万个位置的存储空间。

1 | |

- 寻址能力

每个存储位置的bit数目为 寻址能力,如 16MB内存,包含约1600万个位置的存储空间,每个位置存储1Byte=8bit信息。

1 | |

1 | |

graph LR;

1[地址宽度/2] --译码器---> 2[寻址空间/2^2];

2 --多路复用器选中---> 3[一个位置/寻址能力-bit/3-bit]

–作业–

有限状态机

特点

-

有限数目的状态

1

A finite number of states. -

有限数目的外部输入

1

A finite number of external inputs. -

有限数目的外部输出

1

A finite number of external outputs. -

显示注明的状态转移

1

An explicit specification of all state transitions. -

显示注明的对外输出

1

An explicit specification of what determines each external output value.–作业–

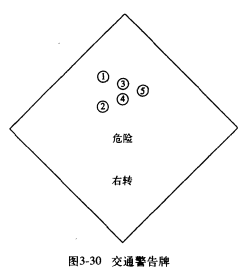

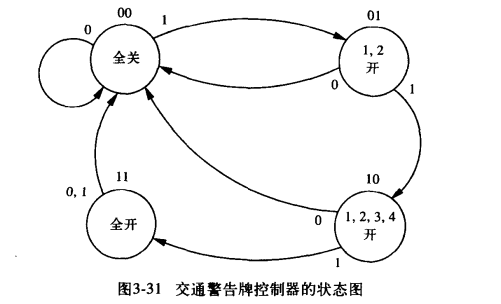

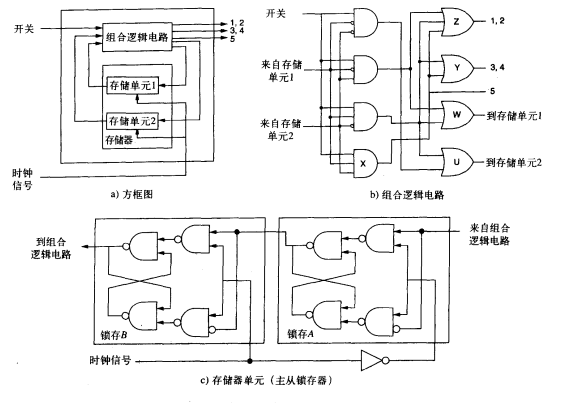

时序逻辑电路

例:交通警告牌的时序逻辑电路

逻辑说明

逻辑实现

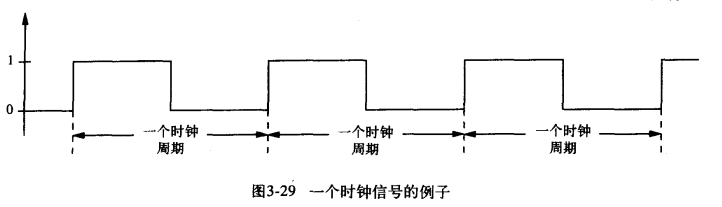

- 触发机制:时钟

状态转移通过时钟电路触发,时钟电路具有周期性,当 低电平0 转换为 高电平1,下一周期开始,状态转移。

-

组成部分

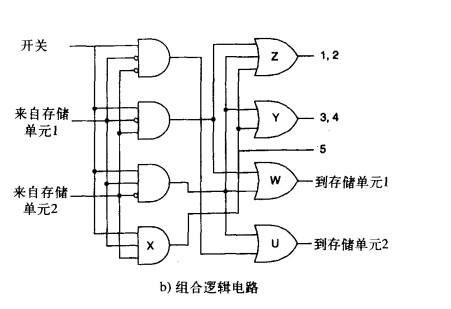

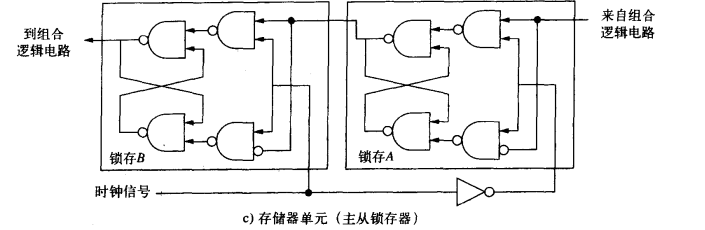

组成部分 电路图示例 功能 组合逻辑电路

实现输入与记忆状态到输出与下一记忆状态的状态转移 存储器单元

使用两个主从锁存器组成一个存储器单元,以避免状态在当前周期即被瞬时覆盖的问题

–作业–

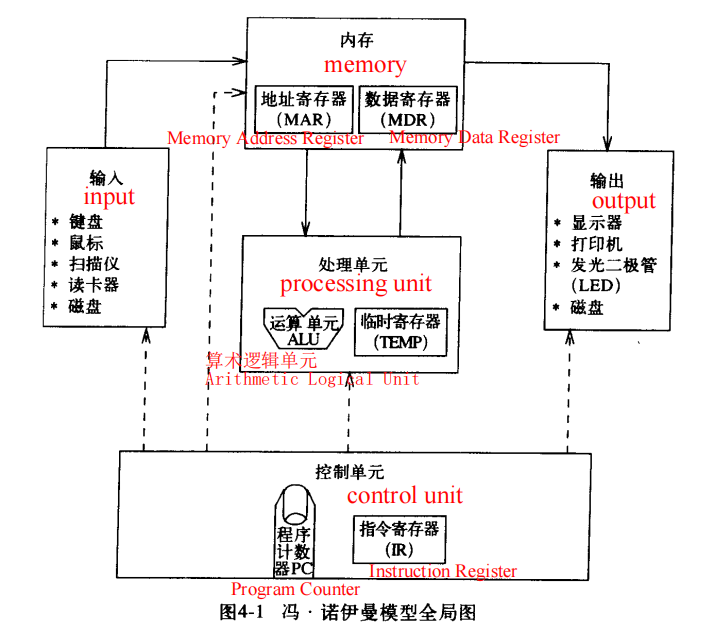

冯诺伊曼模型

1)名词

| 英文 | 中文 | 释义 |

|---|---|---|

| The Von Neumann Model | 冯诺伊曼模型 | |

| input/output/memory/processing unit/control unit | 输入/输出/内存/处理单元/控制单元 | |

| instruction | 指令 | |

| opcode | 操作码 | |

| operand | 操作数 | |

| source register | 源寄存器 | SR |

| destination register | 目的寄存器 | DR |

| instruction cycle | 指令周期 | |

| phase | 指令节拍 | |

| FETCH | 取指令 | |

| DECODE | 译码 | |

| EVALUATE ADDRESS | 地址计算 | |

| FETCH OPERAND | 取操作数 | |

| EXECUTE | 执行 | |

| STORE RESULT | 存放结果 | |

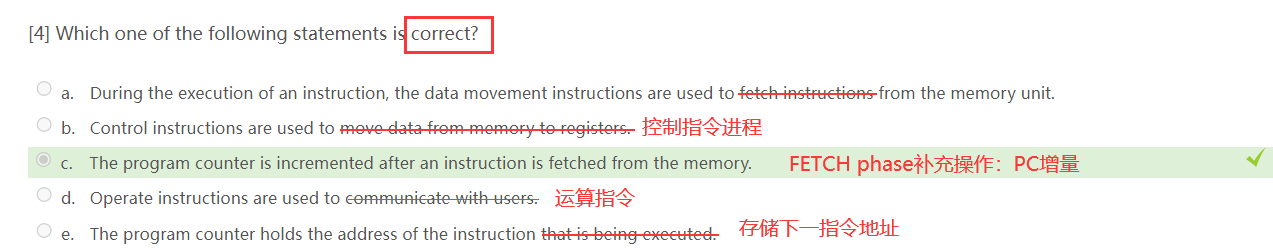

| operate instruction | 运算指令 | 顺序 |

| data movement instruction | 数据搬移指令 | 顺序 |

| control instruction | 控制指令 | 循环 |

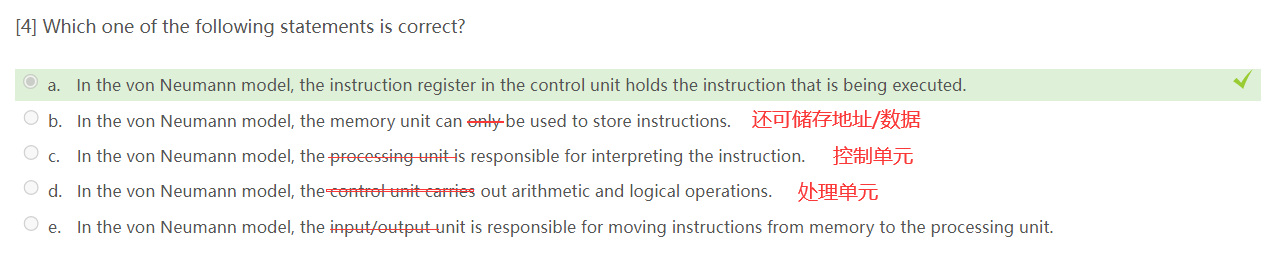

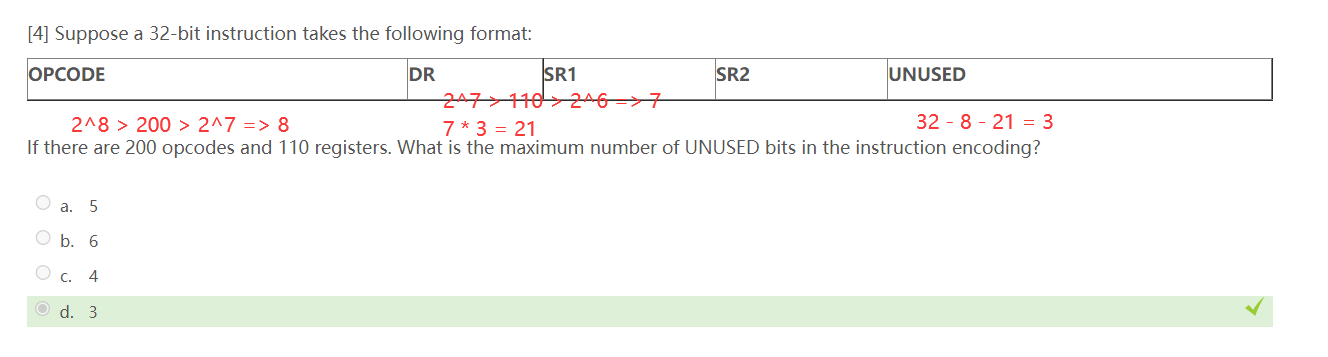

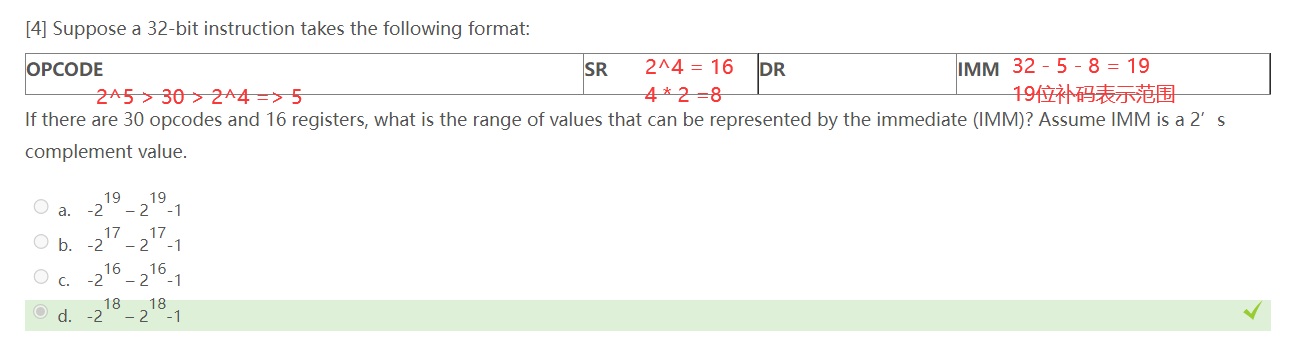

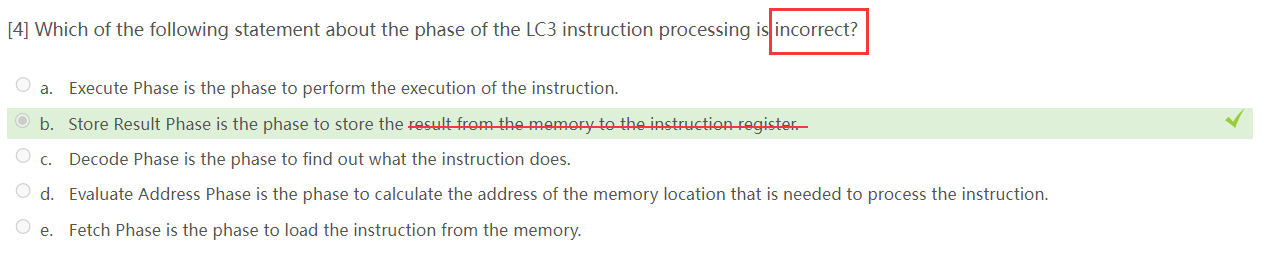

2)知识点

考点总结

- 冯诺依曼模型各个组成部分及其功能对应判断

- 不同指令类型格式各切片段对应意义 计算位数

- 指令周期各节拍功能对应判断

模型组成

–作业–

指令类型格式

graph LR;

1[指令] --> 操作码opcode/指令具体内容;

1 --> 操作数operand/操作对象

指令类型与对应指令格式

-

运算指令(操作码OPCODE–目的寄存器DR–源寄存器SR–UNUSED)

–作业–

-

数据搬移指令(操作码OPCODE–源寄存器SR–目的寄存器DR–寻址方式)

–作业–

-

控制指令

指令周期

| phase | ||

|---|---|---|

| FETCH | 取指令 | |

| DECODE | 译码 | |

| EVALUATE ADDRESS | 地址计算 | |

| FETCH OPERAND | 取操作数 | |

| EXECUTE | 执行 | |

| STORE RESULT | 存放结果 |

-

FETCH 取指令

1

Load next instruction (at address stored in PC) from memory into Instruction Register (IR).graph LR; 0[控制单元PC寄存器] --下一指令地址---> 1[内存MAR地址寄存器]; 1 --下一指令地址---> 2[内存]; 2 --下一指令---> 3[内存MDR数据寄存器]; 3 --下一指令---> 4[控制单元IR寄存器]; 0[控制单元PC寄存器] --PC增量/更新下一指令---> 0; -

DECODE 译码

1

2

3First identify the opcode.

* In LC-3, this is always the first four bits of instruction.

* A 4-to-16 decoder asserts a control line corresponding to the desired opcode.

graph LR;

0[控制单元IR寄存器] --指令操作码---> 1[译码器];

1 --选中指令---> 1;

-

EVALUATE ADDRESS 地址计算

1

For instructions that require memory access, compute address used for access.graph LR; 0[控制单元IR寄存器] --指令操作数---> 1[译码器] --地址值---> 1; -

FETCH OPERAND 取操作数

1

Obtain source operands needed to perform operation.graph LR; 译码器 --地址值---> 1[内存MAR地址寄存器] --地址值---> 2[内存]; 2 --地址对应数据---> 3[内存MDR数据寄存器] -

EXECUTE 执行

1

Perform the operation, using the source operands.graph LR; 译码器 --指令---> 1[处理单元ALU] --执行结果---> 1; 内存MDR数据寄存器 --数据---> 1 -

STORE RESULT 存放结果

1

Write results to destination.(register or memory)graph LR; 1[处理单元ALU] --执行结果---> 目的寄存器;

–作业–

LC-3结构及其ISA

1)名词

| 英文 | 中文 | 释义 |

|---|---|---|

| Instruction Set Architecture | 指令集结构 | |

| Addressing Modes | 寻址模式 | |

| immediate | 立即数寻址 | non-memory address |

| register | 寄存器寻址 | non-memory address |

| PC-relative | 相对寻址 | memory address |

| indirect | 间接寻址 | memory address |

| base+offset | 基址偏移 | memory address |

| load | 装载 | 数据从内存移入寄存器 |

| store | 存储 | 数据从寄存器转入内存 |

| condition code | 条件码 |

2)知识点

ISA概述

1 | |

graph LR;

0[ISA的构成] --- 1[内存 Memory];

0 --- 2[寄存器 Register];

2 -.- 为了减少读取内存时间的临时存储空间;

0 --- 3[指令集 Instruction Set];

3 --- 3.1[操作码 Opcode];

3 --- 3.2[数据类型 Data Type];

3 --- 3.3[寻址模式 Addressing Modes];

3.1 -.- 操作指令;

3.1 -.- 数据搬移指令;

3.1 -.- 控制指令;

3.2 -.- 补码整数;

3.3 -.- 4[非内存寻址];

3.3 -.- 5[内存寻址];

4 -.- 立即数寻址;

4 -.- 寄存器寻址;

5 -.- 相对寻址;

5 -.- 间接寻址;

5 -.- 基址偏移;

指令及其寻址模式

操作码对译

| 操作码 | 指令 | 寻址方式 |

|---|---|---|

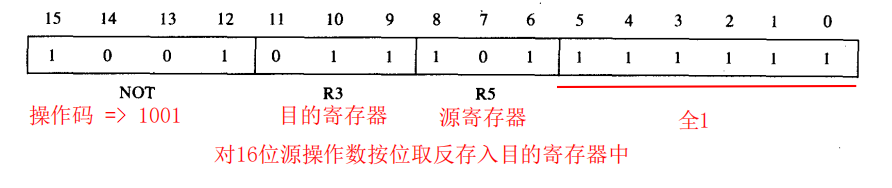

| 1001 | NOT | 寄存器寻址 |

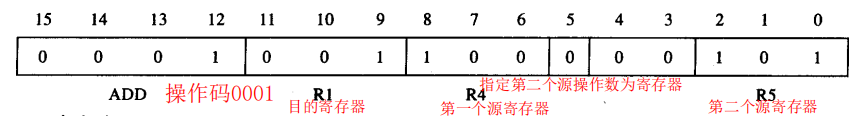

| 0001 (bit[5] = 0) | ADD | 寄存器寻址 |

| 0001 (bit[5] = 1) | ADD | 立即数寻址 |

| 0101 (bit[5] = 0) | AND | 寄存器寻址 |

| 0101 (bit[5] = 1) | AND | 立即数寻址 |

| 0010 | LD | PC相对寻址 |

| 1010 | LDI | 间接寻址 |

| 0110 | LDR | 基址偏移寻址 |

| 0011 | ST | PC相对寻址 |

| 1011 | STI | 间接寻址 |

| 0111 | STR | 基址偏移寻址 |

| 1110 | LEA | 立即数寻址 |

| 0000 | BR |

操作指令

- NOT 指令 1001:寄存器寻址

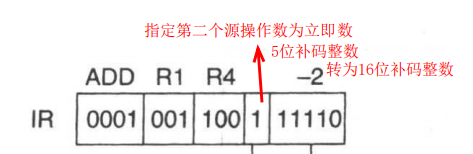

- ADD指令 0001:寄存器寻址/立即数寻址

1. 寄存器寻址

2. 立即数寻址

立即数寻址即操作数可由指令直接获得,而不需要去任何内存/暂存区寻找。

-

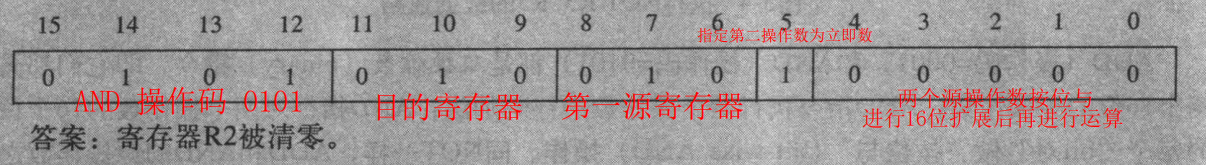

AND指令 0101:寄存器寻址/立即数寻址

-

寄存器寻址

类似于ADD指令 仅操作码更改其它字段意义一样

-

立即数寻址

-

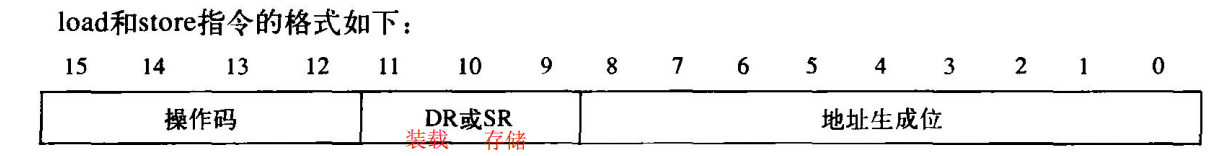

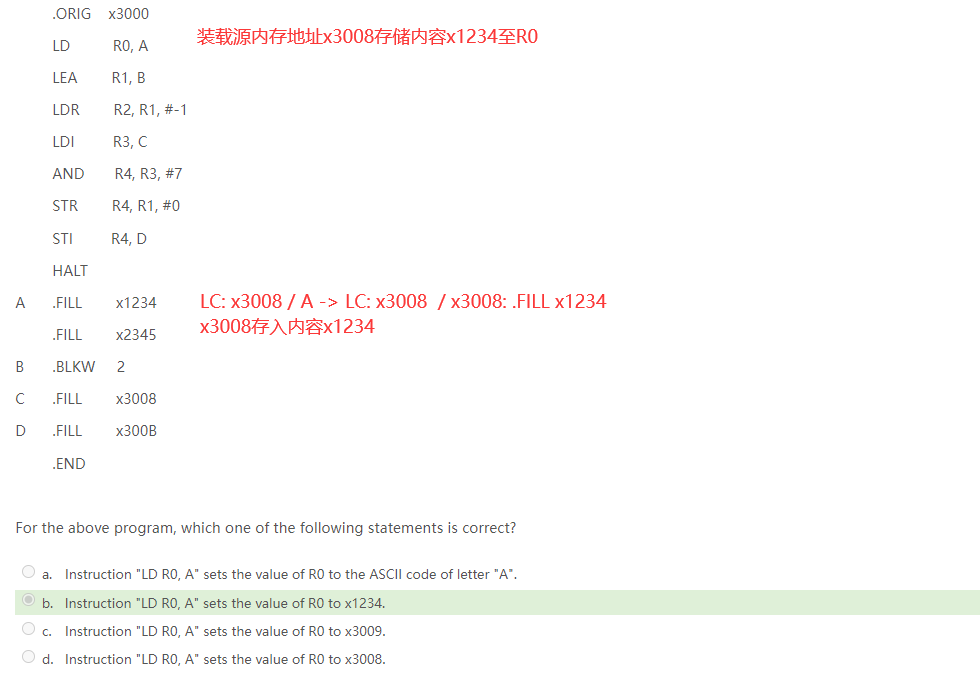

数据搬移指令

数据搬移指令的任务是在通用寄存器(GPR)和内存之间、寄存器和输入/输出设备之间搬动数据。

graph LR;

寄存器 --存储--> 内存;

内存 --装载--> 寄存器

数据搬移指令的一般格式

装载LD/存储ST/有效地址装在LEA:PC相对寻址/间接寻址/基址偏移寻址/立即数寻址

-

PC相对寻址

1

2

3the offset which is 9 bits available for address convert to 16 bits and plus with PC after its' increment.

9 bits: -256 <= offset <= +255

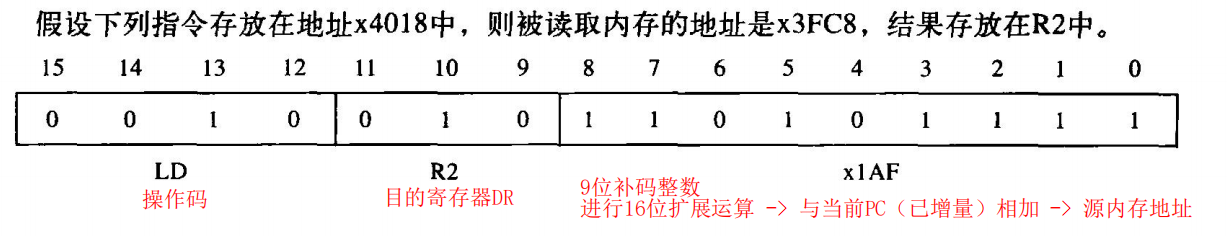

the address limit: PC - 256 <= memory <= PC +255LD指令 0010

ST指令 0011

1

2

3

4

5

6

7

81. 对于补码整数求16位扩展,若首位为1则在首位前补齐1,首位为0则在首位前补齐0

16位扩展转为16进制

求得偏移值

1 1010 1111 -> 1111 1111 1010 1111 -> xFFAF

2. 偏移值与已增量PC相加

求得源内存地址

x4018 -> x4019

x4019 + xFFAF -> x3FC8 -

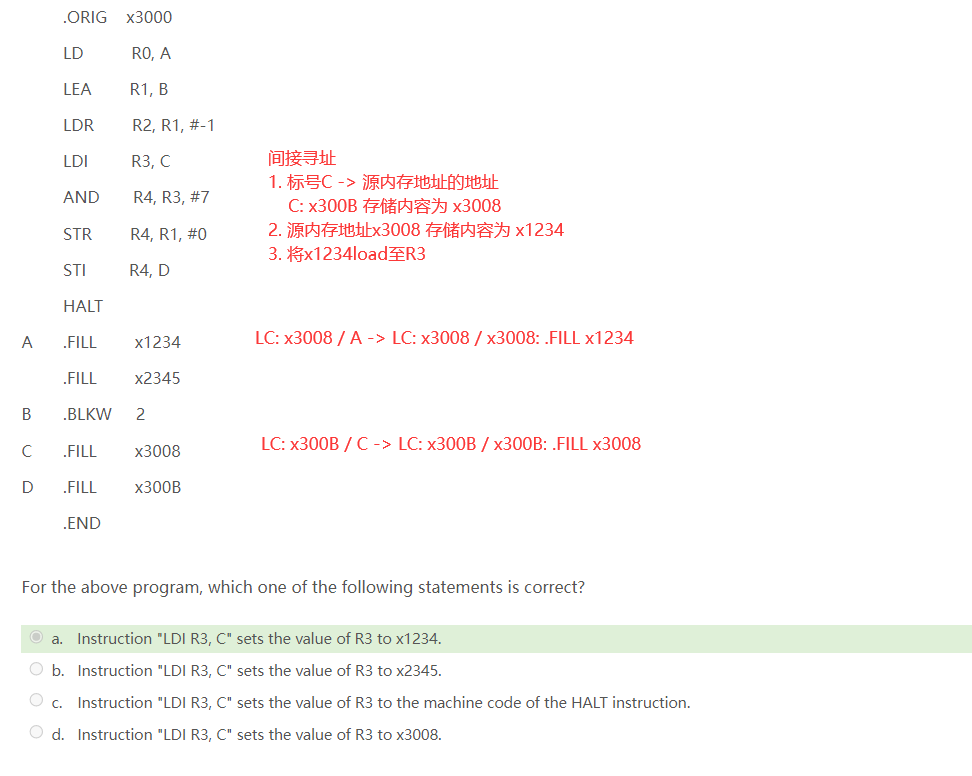

间接寻址

1

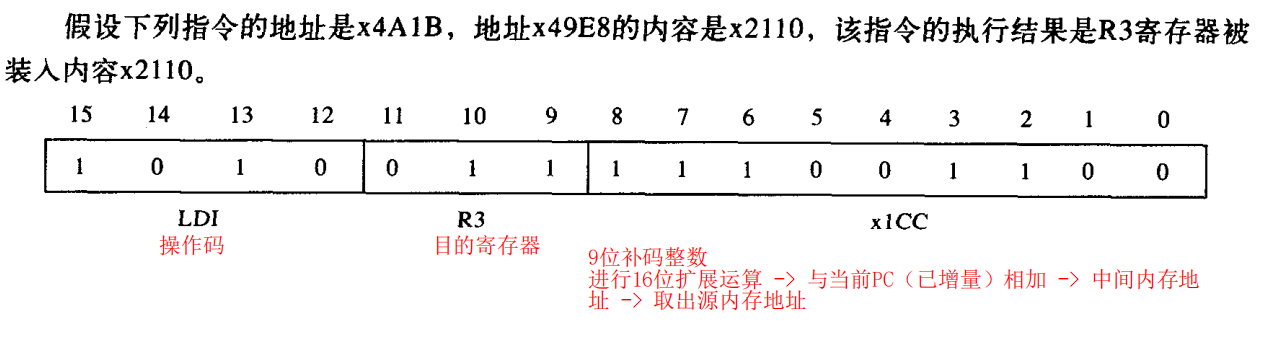

First address is generated from PC and IR(just like PC-relative addressing), then content of that address is used as target for load/store.LDI指令 1010

STI指令 1011

1

2

3

4

5

6

7

8

91. 对于补码整数求16位扩展,若首位为1则在首位前补齐1,首位为0则在首位前补齐0

16位扩展转为16进制

求得偏移值

1 1100 1100 -> 1111 1111 1100 1100 -> xFFCC

2. 偏移值与已增量PC相加

求得源内存地址

x4A1B -> x4A1C

x4A1C + xFFCC -> x49E8

3. 读取x49E8内容即为源内存地址:x2110 -

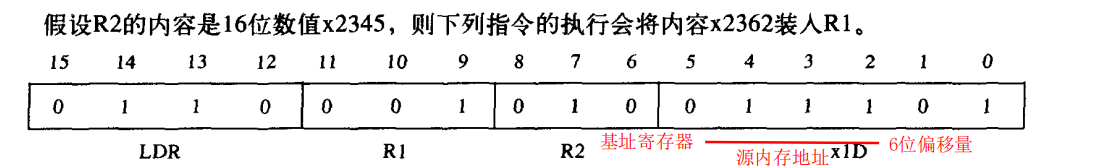

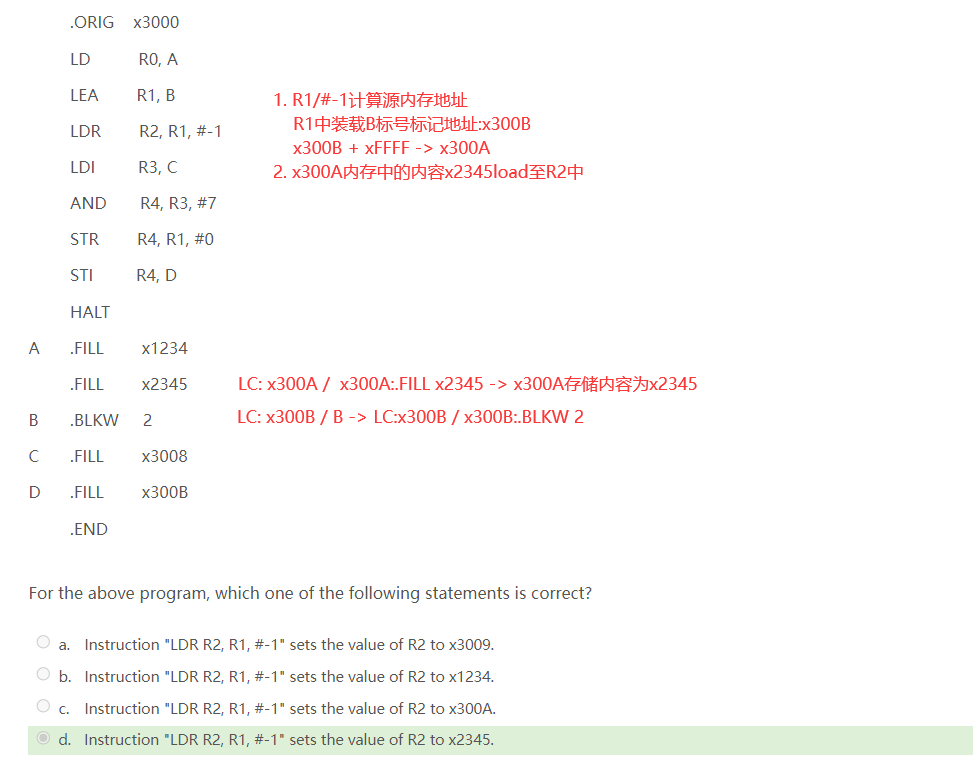

基址偏移寻址

LDR指令 0110

STR指令 0111

1

2

3

4

5

6

71. 对于补码整数求16位扩展,若首位为1则在首位前补齐1,首位为0则在首位前补齐0

16位扩展转为16进制

求得偏移值

01 1101 -> 0000 0000 0001 1101 -> x001D

2. 读取R2内容x2345

x2345 + x001D -> x2362

3. 读取x2362装入x0F0F装入R1 -

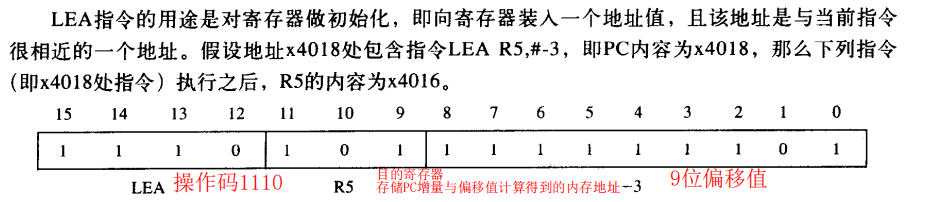

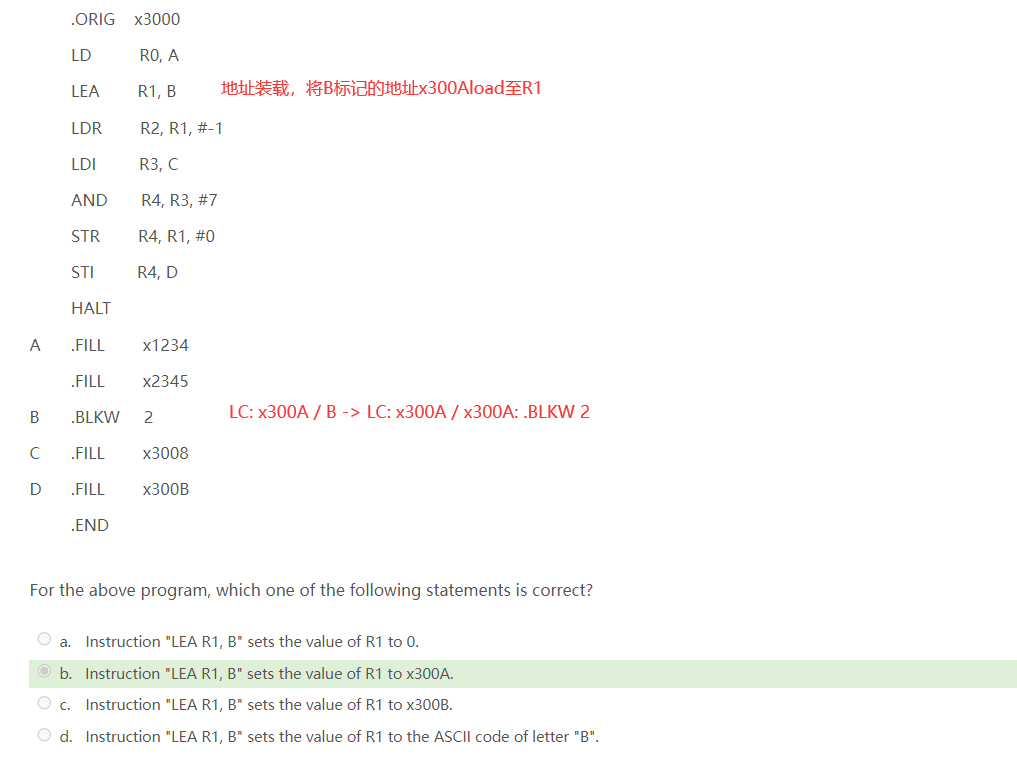

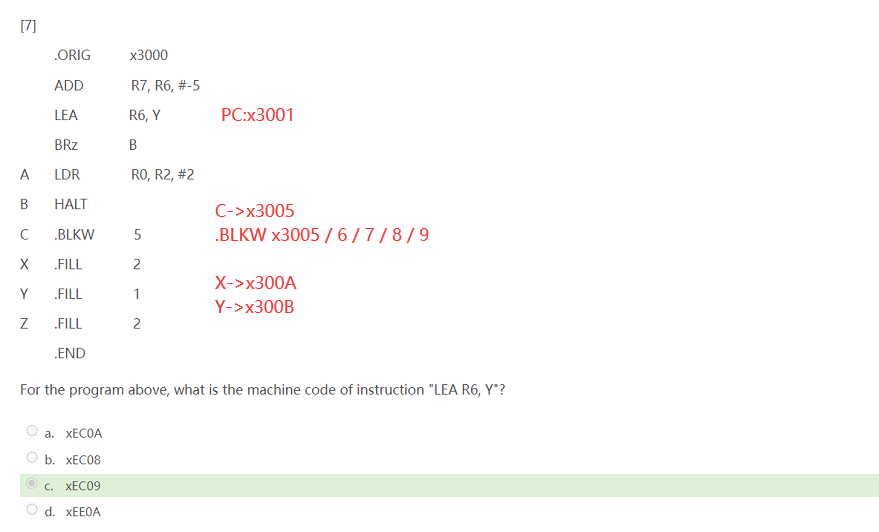

立即数寻址

有效地址装载指令LEA 1110

1

2

3

4

5

61.对于补码整数求16位扩展,

1 1111 1101 -> 1111 1111 1111 1101 -> xFFFD

2.PC增量 + 偏移值

x4019 + xFFFD -> x4016

3.将计算得到的内存地址存入目的寄存器

R5 -> x4016

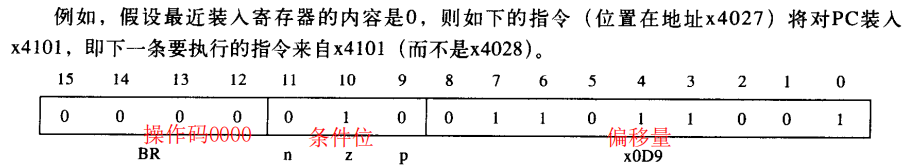

控制指令

条件跳转指令BR 0000

1 | |

1 | |

–作业–

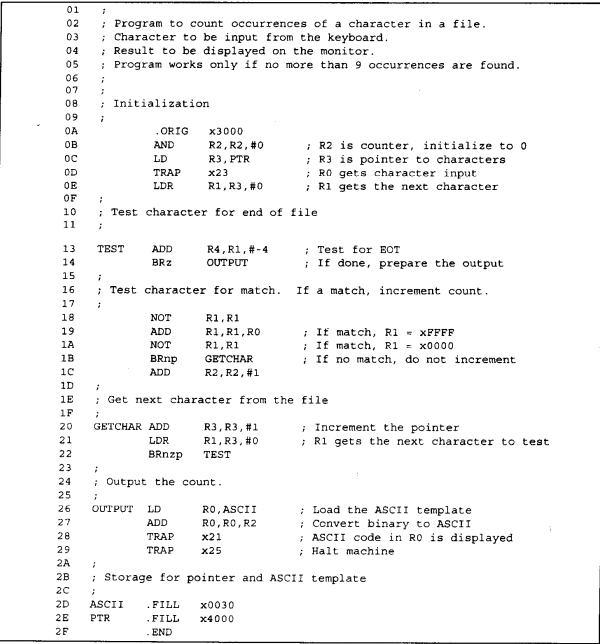

汇编语言

1)名词

| 英文 | 中文 | 释义 |

|---|---|---|

| instruction | 指令 | |

| comment | 注释 | |

| assember directive (pseudo-op) | 汇编指令/伪操作 | |

| optional/mandatory | 可选的/必需的 | |

| assembler | 汇编器 | |

| assembly | 汇编 | |

| Location Center(LC) | 地址跟踪计数器 |

2)知识点

考点总结

-

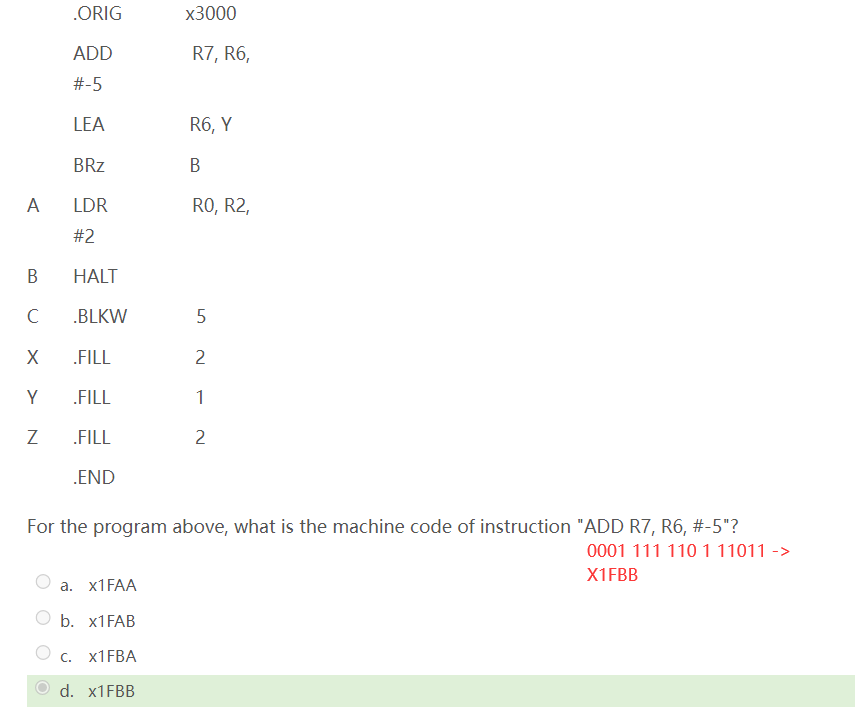

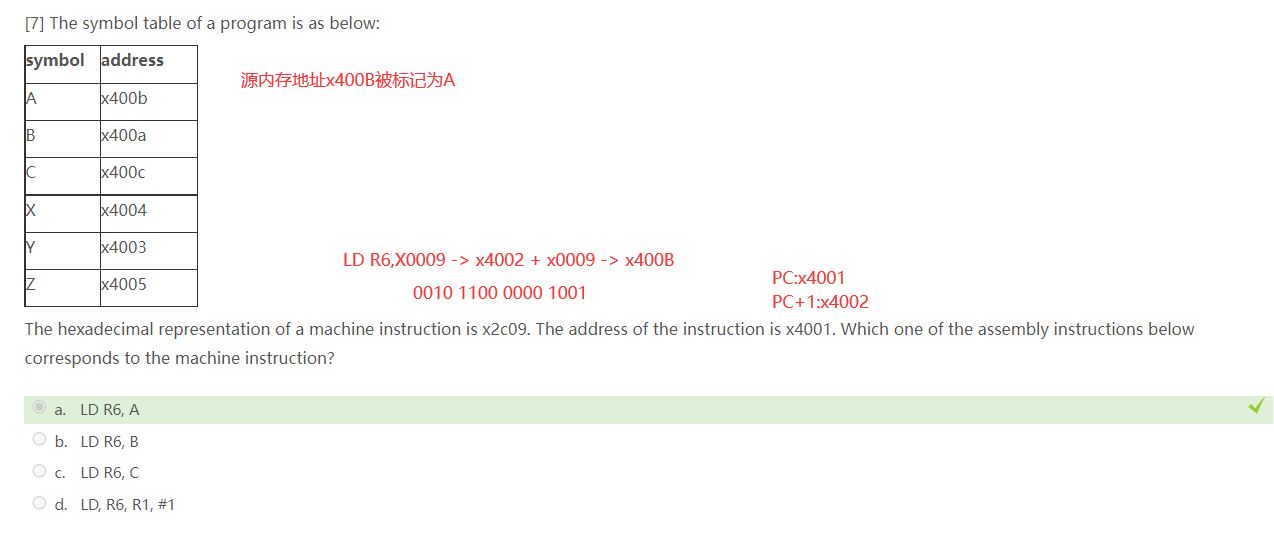

指令转机器码

-

机器码转指令

-

解读汇编程序

-

伪操作

-

指令

1

2

3

4判断指令类型,如

* 地址装载:装载标号标记的地址

* 内容装载:装载标号标记的地址中的存储内容

* 间接寻址:装载标号标记的地址中存储的地址中的存储内容

-

-

编写汇编程序

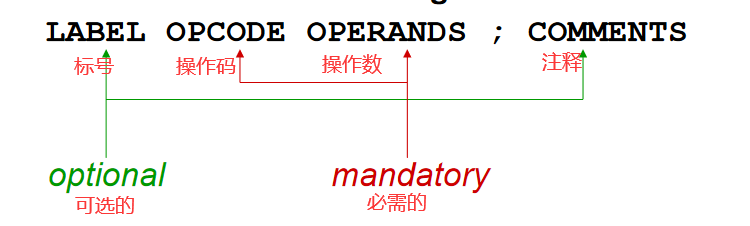

汇编语言的构成

汇编程序被称作 汇编器, 翻译过程称为 汇编,汇编语言由以下三个部分构成

注释

1 | |

指令

一条指令的构成

-

关于标号:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15指向内存单元的一个符号名,类似于标记地址的变量在程序中被引用。

* 赋值

汇编程序采用地址跟踪计数器(LC),从.ORIG伪操作标识地址开始,每成功识别一条有效指令,LC增量。如果该指令行头部存在“标识”字段,则为该标识创建符号表项即二元组[符号,地址值],其中地址值就是LC计数器的当前内容。

e.g:

.ORIG X3000

AND R2,R2,#0

TEST ADD R4,R2,#-1

得到符号表:

TEST x3001

* 引用

需要显示访问内存时将被引用

1)跳转指令的跳转内存地址

2)load/store指令的访问内存地址 -

关于 操作码/操作数:

与机器指令各个字段意义的格式一致,一般包括操作/目的(源)寄存器/访问内存/;立即数

立即数的标识符表示其进制

1

2

3#十进制

b二进制

x十六进制对于比较特殊的TRAP指令,我们可以将其如下表示:

代码 指令 意义 HALT TRAP x25 Halt execution and print message to console.

停止执行并将消息打印到控制台。IN TRAP x23 Print prompt on console, read (and echo) one character from keybd. Character stored in R0[7:0].

在控制台打印提示符,从键盘读取并回显一个字符,存储在R0。OUT TRAP x21 Write one character (in R0[7:0]) to console.

向控制台写入一个字符(在R0)。GETC TRAP x20 Read one character from keyboard. Character stored in R0[7:0].

从键盘读取一个字符,字符存储在R0。PUTS TRAP x22 Write null-terminated string to console. Address of string is in R0.

将以空字符结束的字符串写入控制台。字符串的地址在R0中。

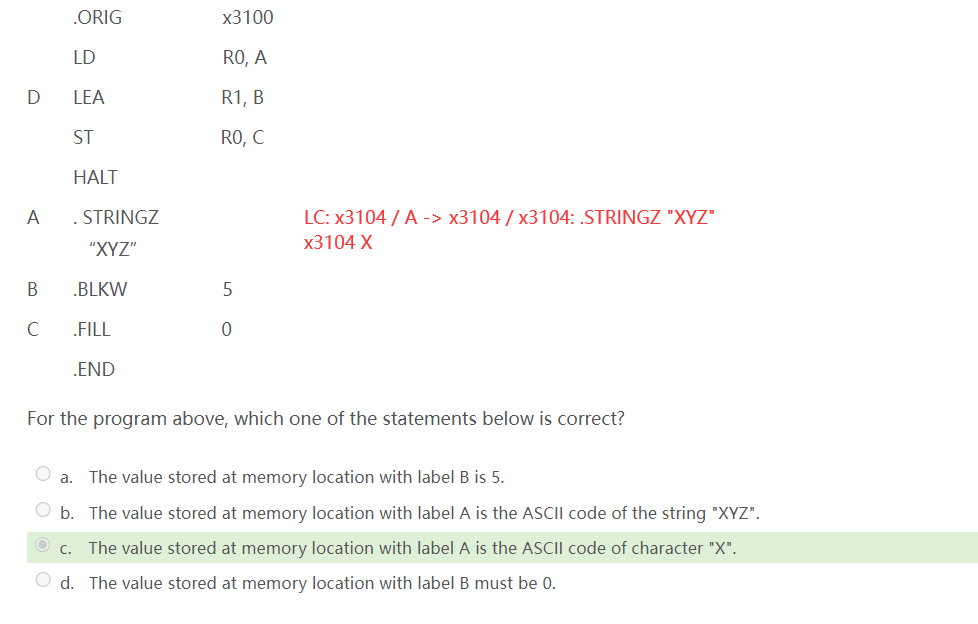

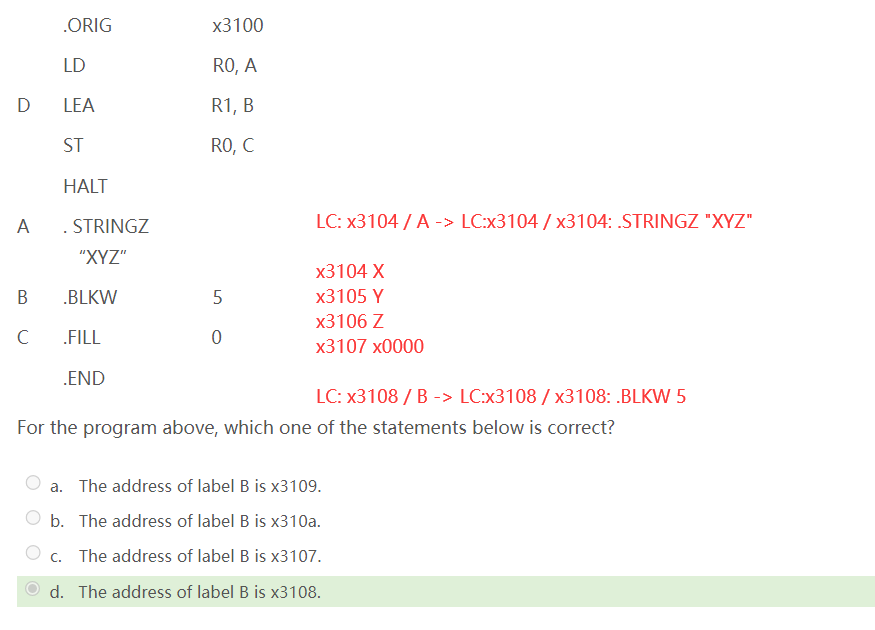

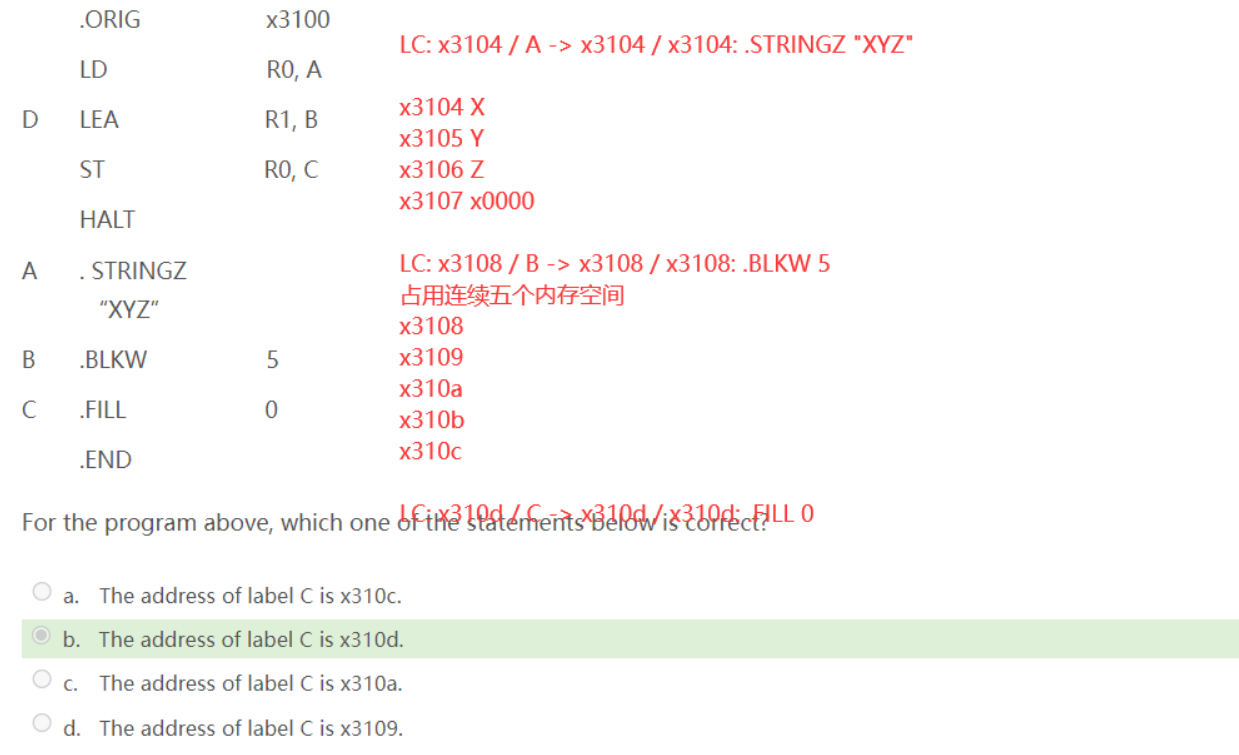

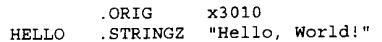

伪操作

1 | |

伪操作的构成与指令类似,由 标号(可选)、伪操作、地址/操作对象 组成,一般用来标记内存地址

| LC-3汇编器的伪操作 | 意义 | 释义 |

|---|---|---|

| .ORIG | 汇编程序开始的内存地址 | .ORIG x3000 程序从PC: x3000开始 |

| .FILL | 填充操作数 | .ORIG X3000 AND R2,R2,#0 TEST ADD R4,R2,#-1 PTR .FILL x4000 PTR标记的内存地址x3002被写入x4000 |

| .BLKW | 从当前地址开始分配由操作数决定个数的内存单元空间 | .ORIG X3000 AND R2,R2,#0 TEST ADD R4,R2,#-1 PTR .FILL x4000 |

| .STRINGZ | .从当前连续占用并初始化n+1个内存单元,其参数(或操作数)是双括号括起来的n个字符。 n+1个内存单元的前n个字的内容分别是字符串对应字符的ASCII码的零扩展(zero-extend)值,内存的最后一个字则被初始化为0。 最后的这个字符x0000通常为ASCII码字符串的处理提供了哨兵机制。 |

|

| .END | 程序结束 |

汇编程序的执行过程

两遍扫描

第一遍:构建符号表

-

丢弃注释

-

从

.ORIG开始,对应的初始地址如ORIG所示,并据此将地址跟踪计数器LC初始化。1

LC: x3000 / x3000: AND R2,R2,#0 -

每成功识别出一条有效指令,LC增量(加1)。如果该指令行头部存在“标识”字段,则为该标识创建符号表项即二元组[符号,地址值],其中地址值就是LC计数器的当前内容。

1

2

3

4LC: x3001 / x3001: LD,R3,PTR

LC: x3002 / x3002: TRAP x23

LC: x3003 / x3003: LDR R1,R3,#0

LC: x3004 / TEST -> LCx3004 / x3004: ADD R4,R1,#-4 -

提取符号表

1

2

3

4

5TEST -> x3004

GETCHAR -> x300B

OUTPUT -> x300E

ASCII -> x3012

PTR -> x3013

第二遍:生成机器语言程序

1 | |

[15]:ready bit, 标识输入设备是否可以被读取/输出设备是否可以读取

[14]:interrupt enable bit(IE),

IE置1, 处理器可接受中断信号, 中断驱动I/O

IE置0, 处理器禁止接受中断信号, 轮询I/O

因此,当IE, ready同时置1, 设备就会产生中断信号

1 | |

- 对于陷入矢量求16位扩展

00100011 -> x0023 - 读取该地址的内容, 即服务程序的起始地址

x0023 -> x04A0 - 服务程序执行至"IMP R7"(RET指令)返回用户程序 [链接机制]

1 | |

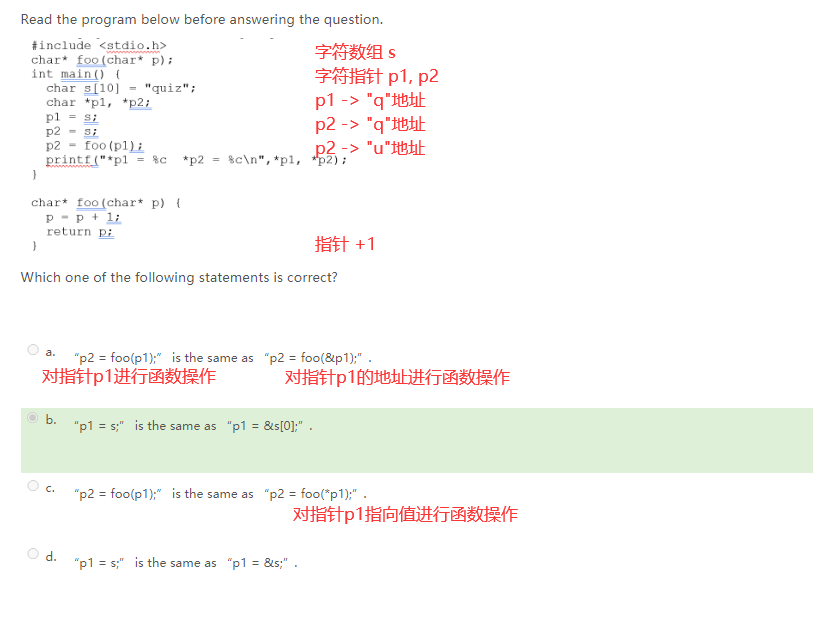

char a[10]; //一维字符数组

char b[5][10]; //二维字符数组

char c[20]={‘c’, ’ ', ‘p’, ‘r’, ‘o’, ‘g’, ‘r’, ‘a’,‘m’}; // 给部分数组元素赋值

//对全体元素赋值(可以省略数组长度)

char d[]={‘c’, ‘.’, ‘p’, ‘r’, ‘o’, ‘g’, ‘r’, ‘a’, ‘m’ };

char d[]={“c.program”};

/* 由于字符串的结束标志是 \0(ASCII0字符) ,由" "包围的字符串会自动在末尾添加,数组化字符串时要注意其长度

char d[]=“c.program”;

1 | |

char p = “c.program”; // 字符型指针用char定义,存储字符串第一个字符的地址

--作业--

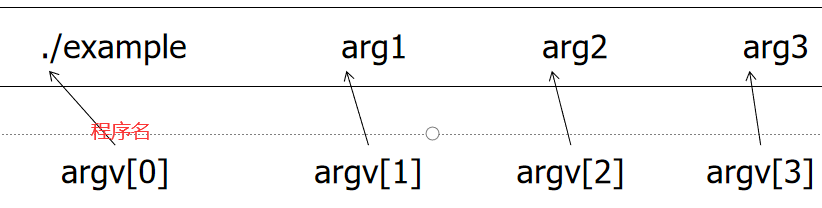

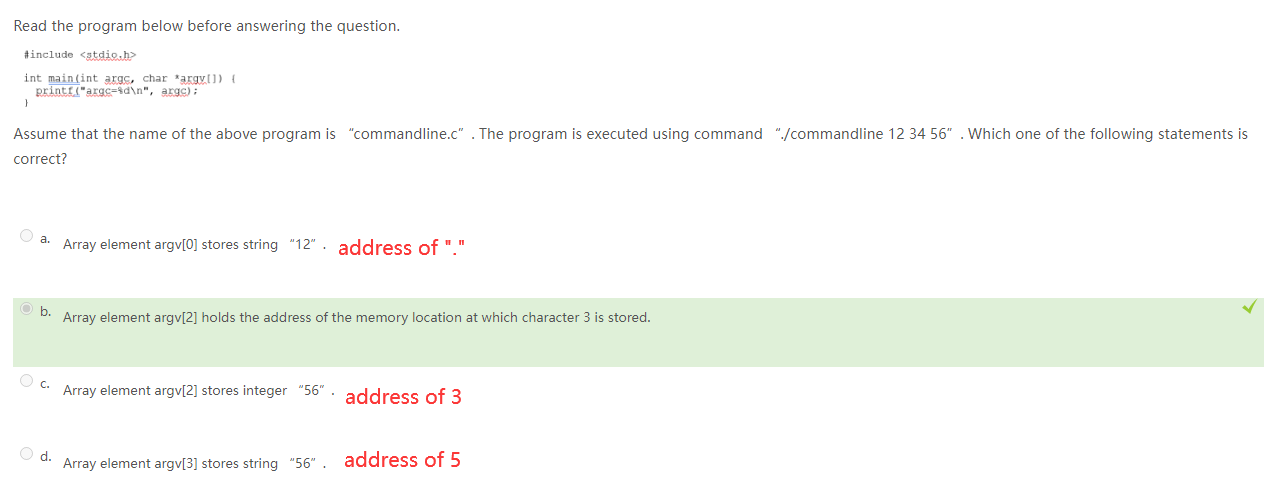

### 命令行参数

**函数参数**

调用程序传递参数给函数,函数中将使用参数的副本。因此函数中参数值更改与其调用程序无关。

**命令行参数**

`int main ( int argc, char *argv[] )`

- `argc `:传给程序的参数个数(包括程序名)

- `argv[]`:参数列表,其中每一个元素对应的是指向每个参数首个地址的指针,对应索引如下

--作业--

<img src="https://raw.githubusercontent.com/TaraTang2003/picgo-typora/main/202206121737606.png" alt="image-20220612173730551" />

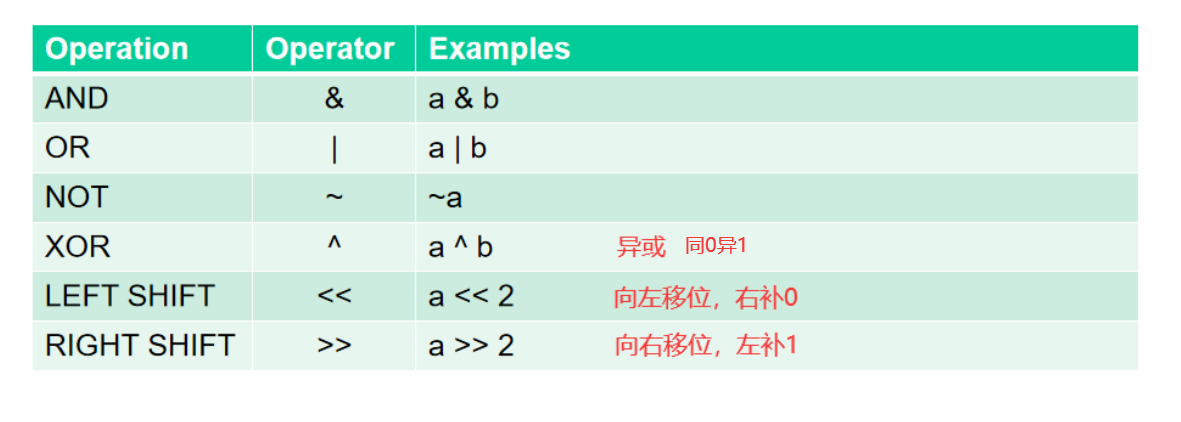

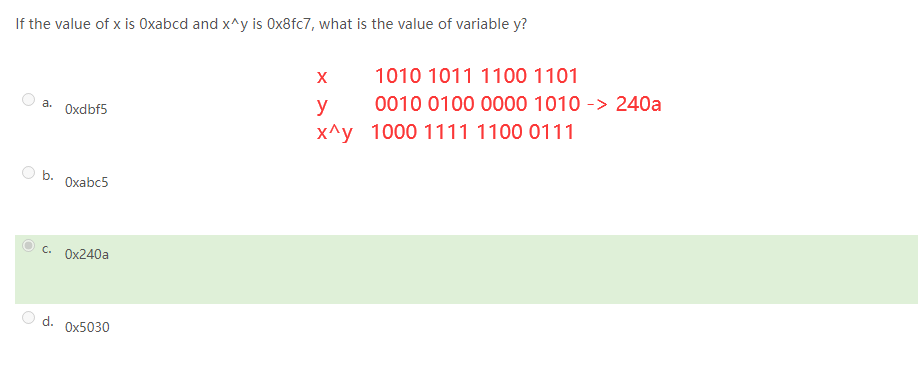

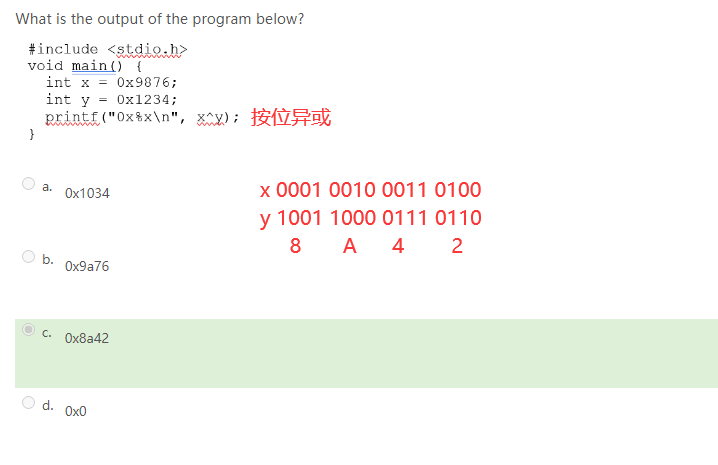

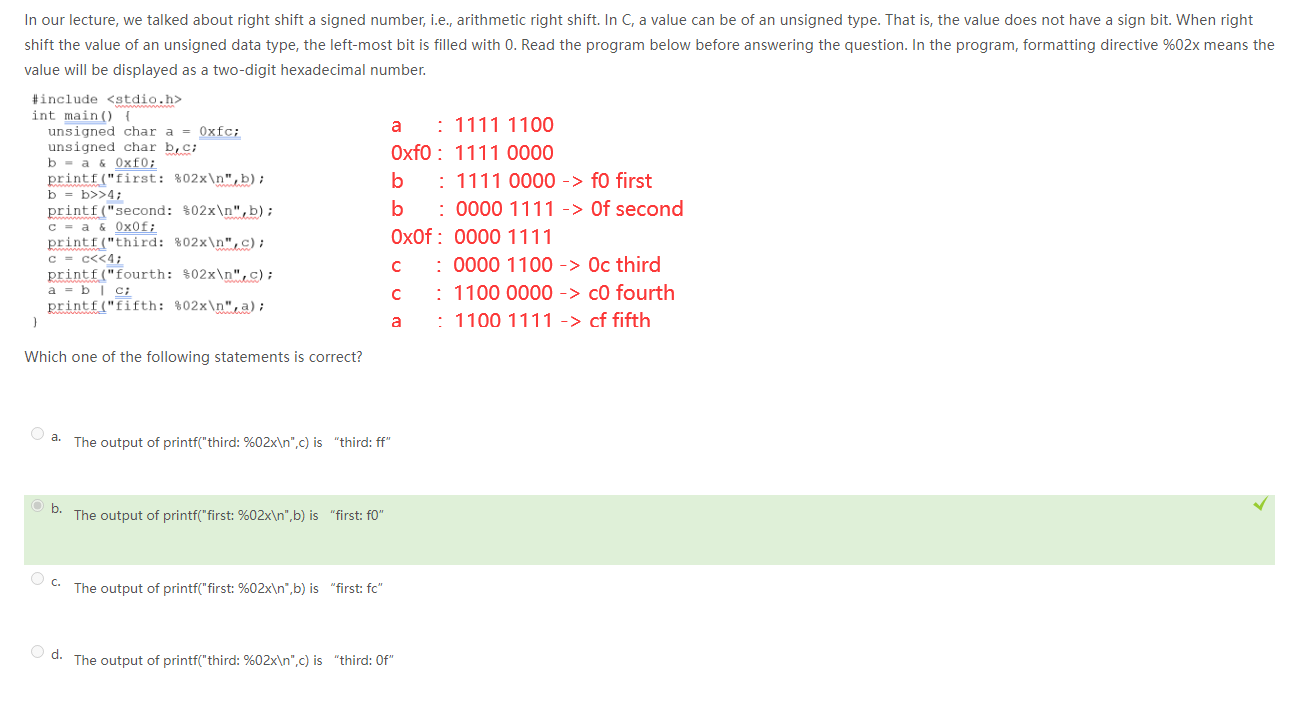

### 位运算符

对两个变量按位运算

--作业--

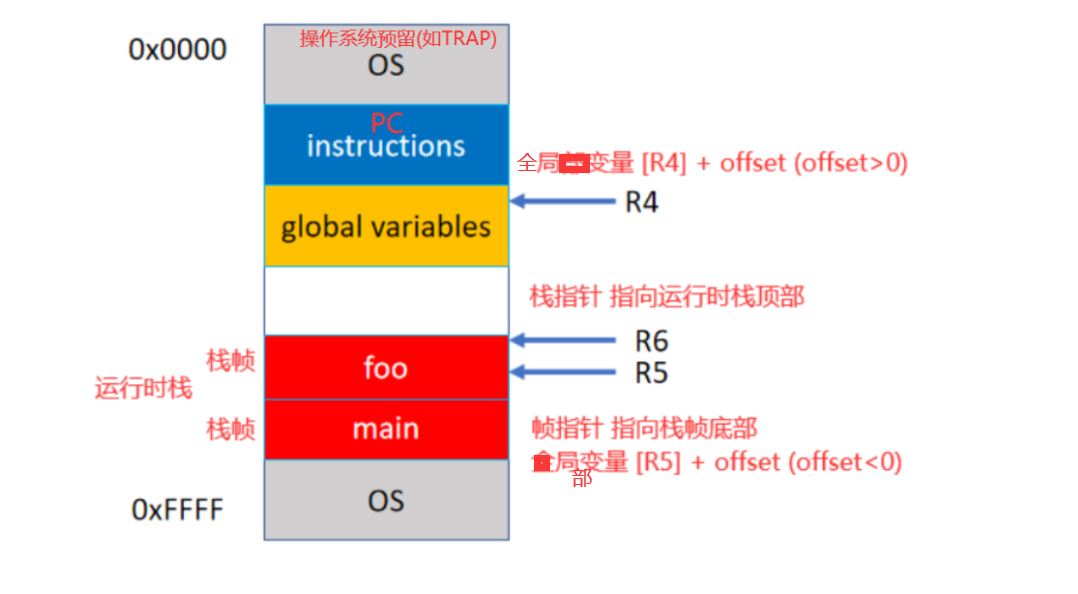

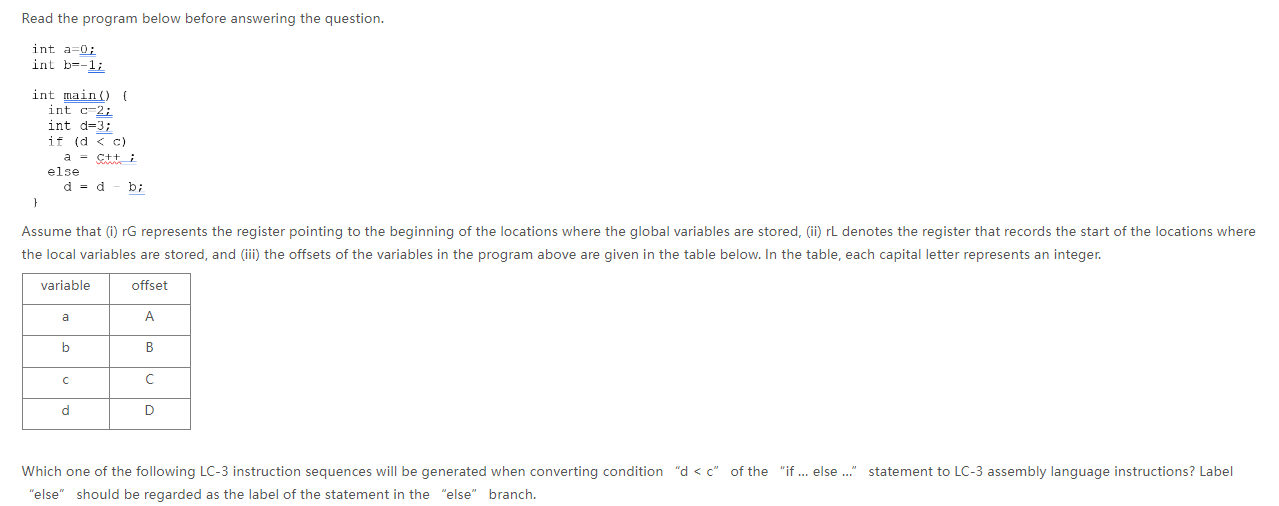

## 运行机制

### 1)名词

| 英文 | 中文 | 释义 |

| ----------------------------------------------------- | --------------------- | ------------------------------------------------ |

| Run-time stack | 运行时栈 | |

| frame pointer | 帧指针 | |

| declaration / function call (invocation) / definition | 函数声明 / 调用/ 定义 | |

| Activation record | 活动记录 | 存储局部变量的栈帧的所在地,帧指针标记其起始地址 |

| bookkeeping | 备忘 | |

| Dynamic link | 动态链 | |

### 2)知识点

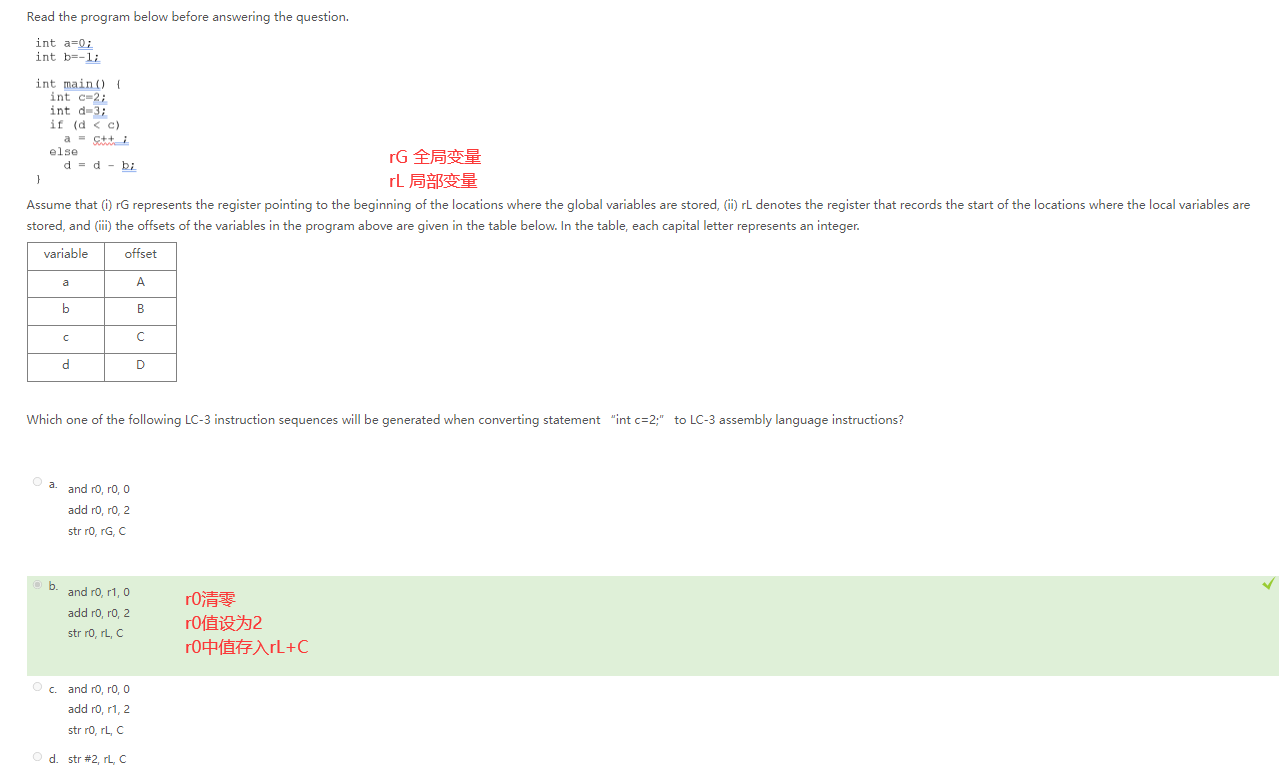

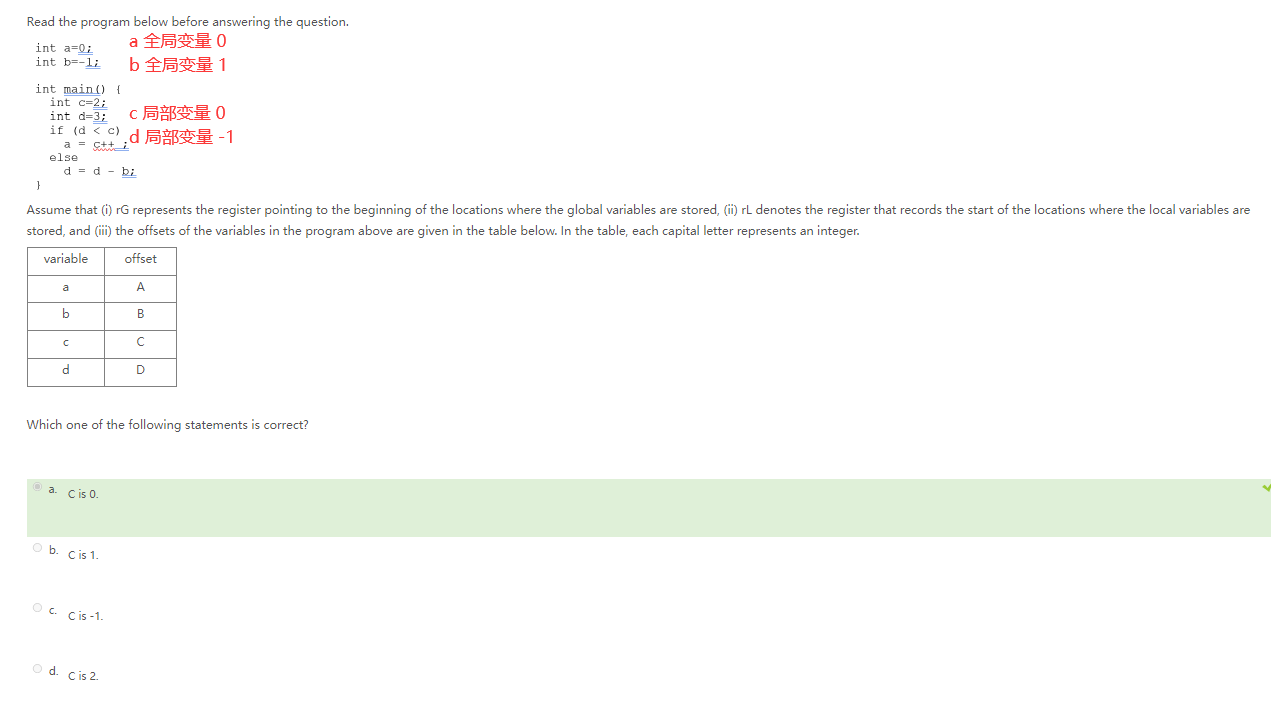

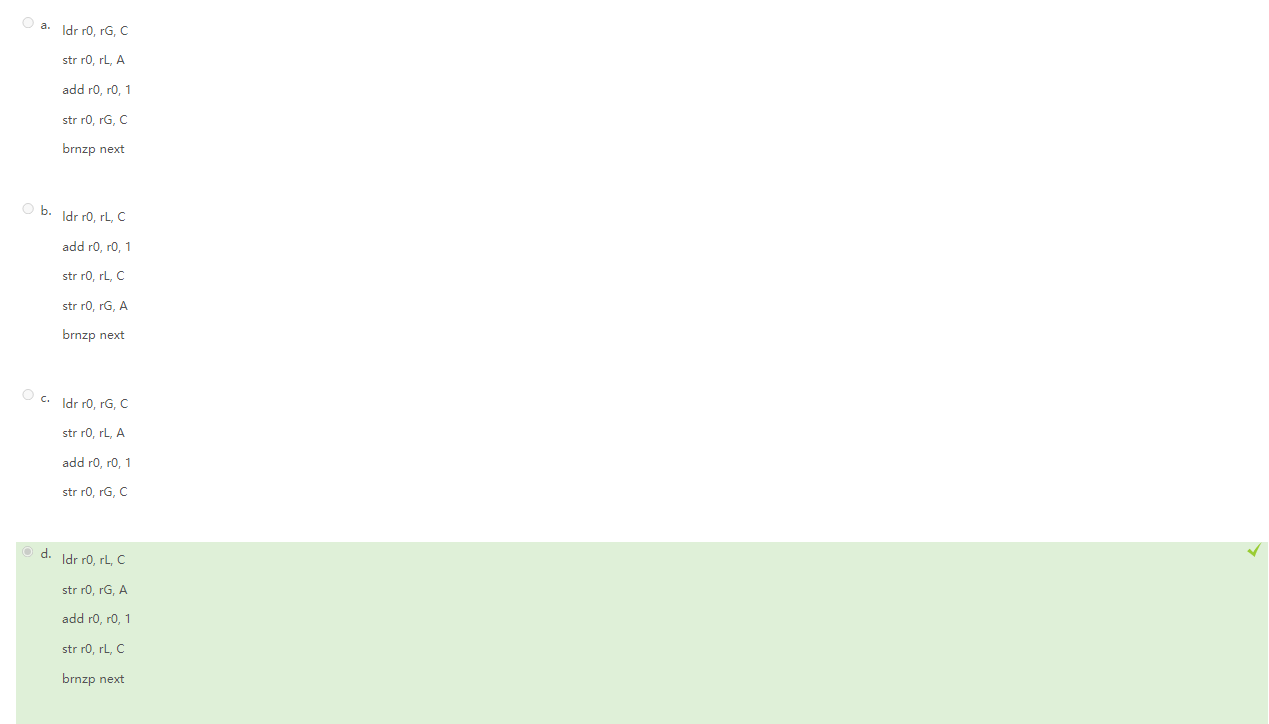

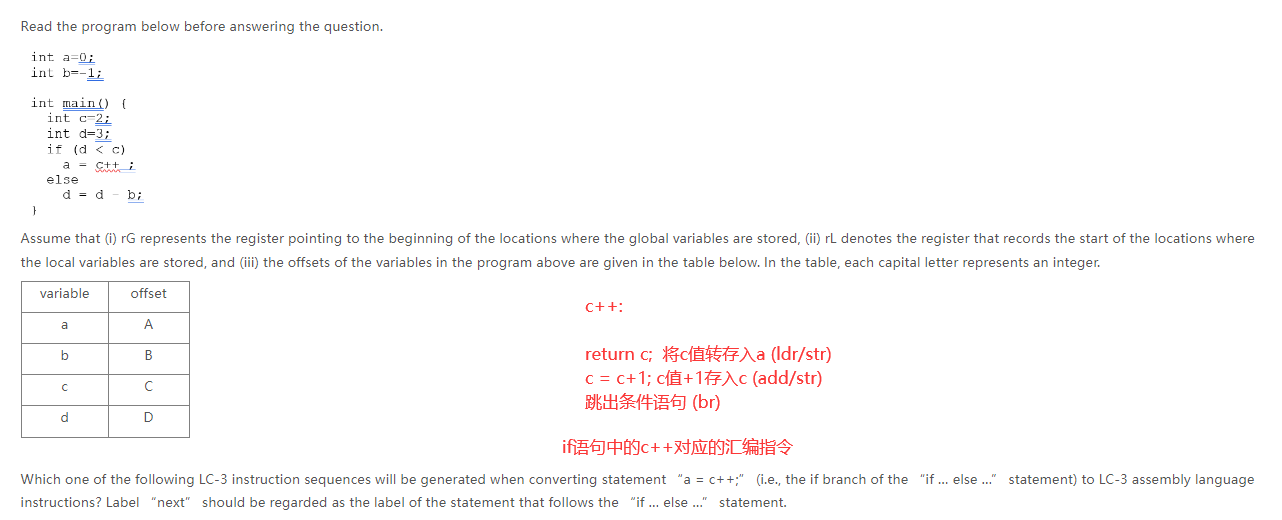

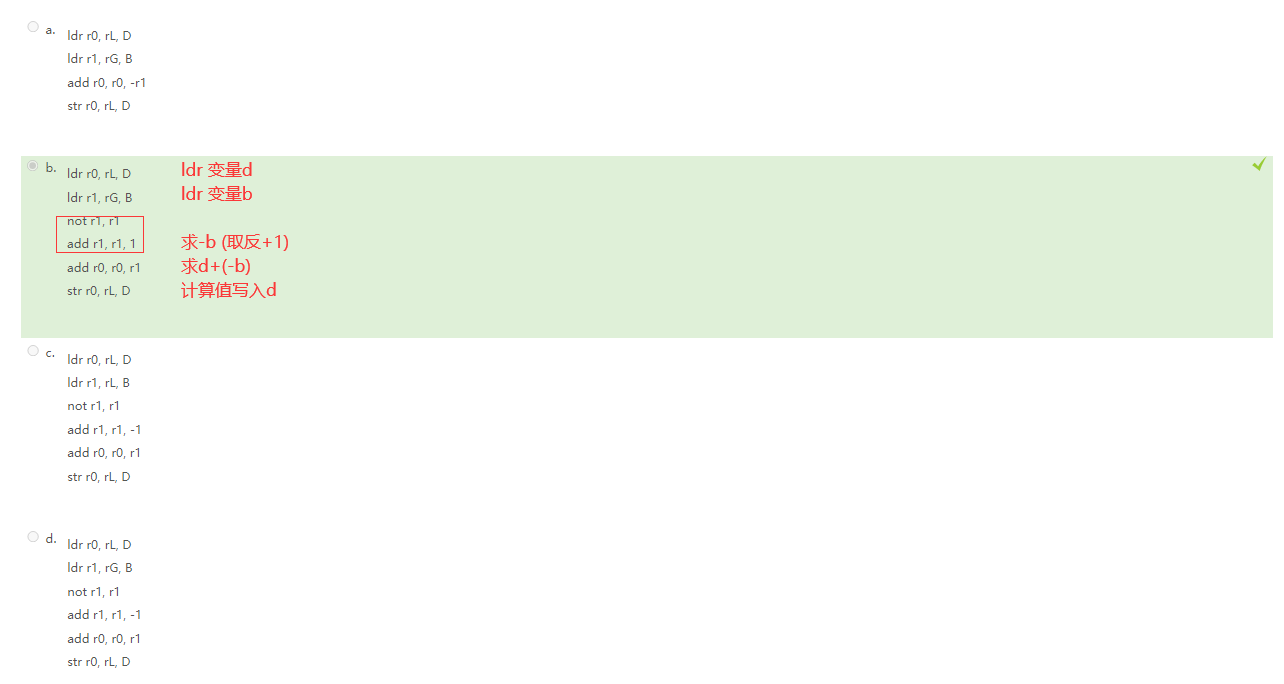

#### 变量的空间分配

--作业 --

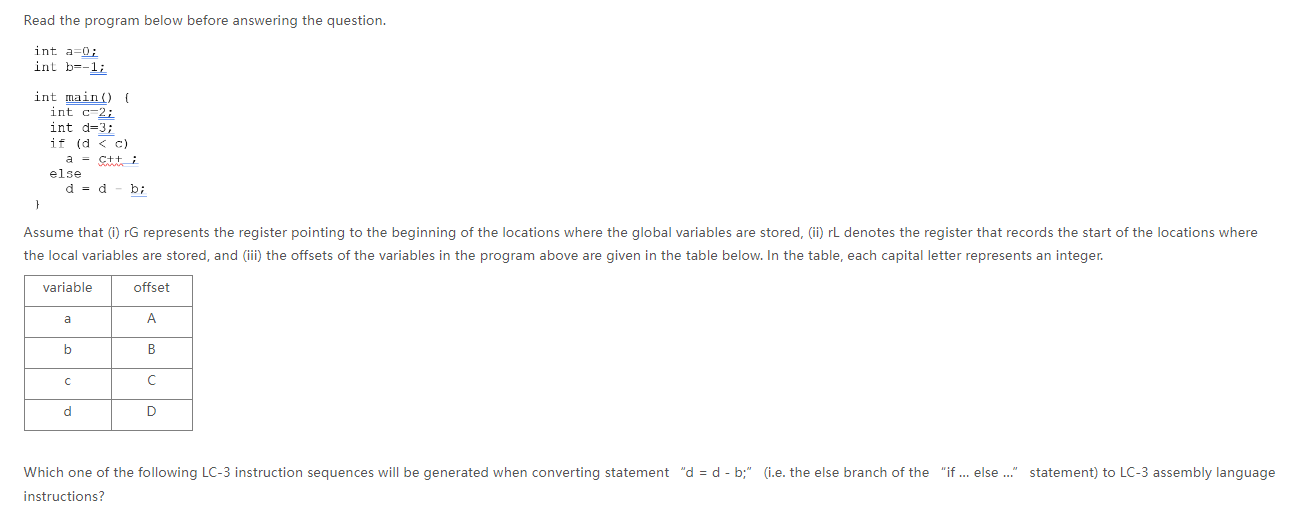

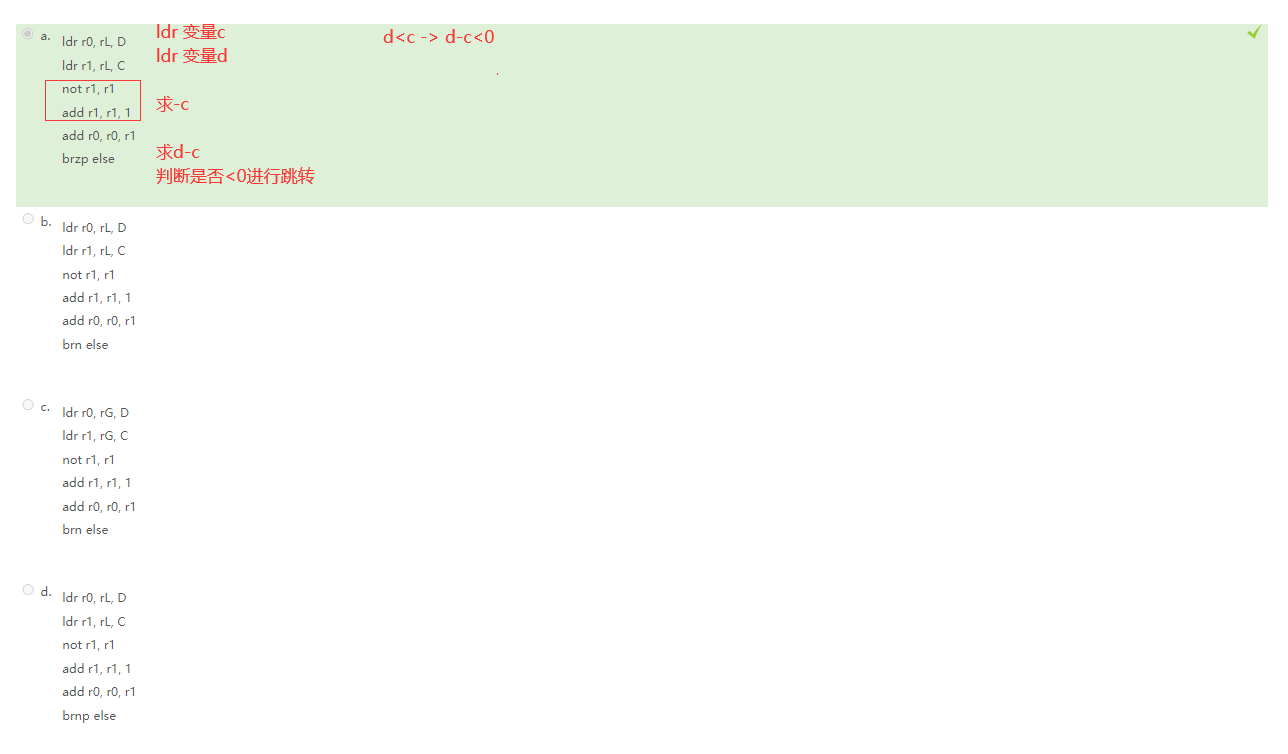

#### 控制结构

--作业--

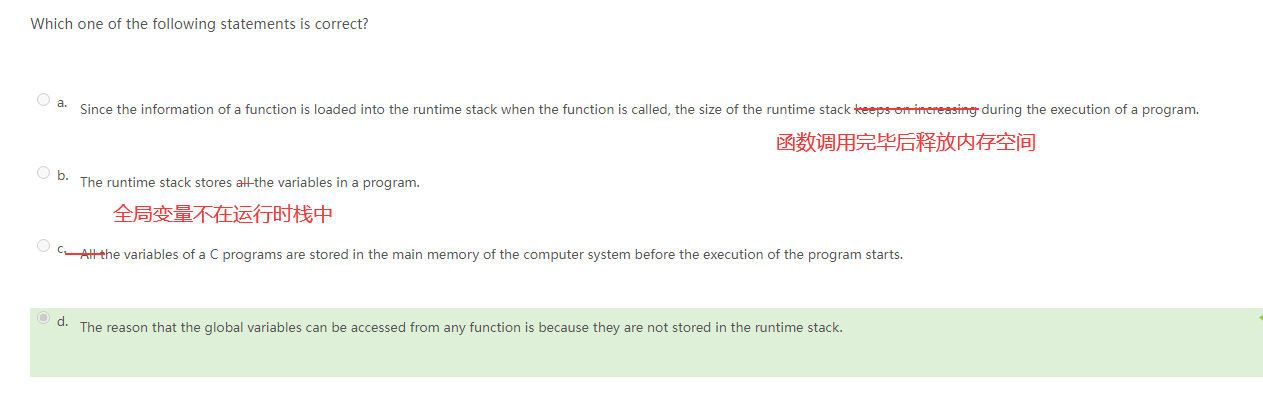

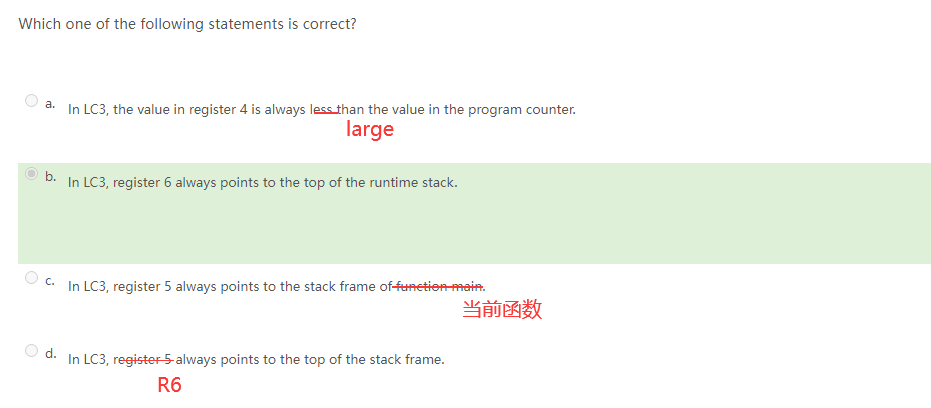

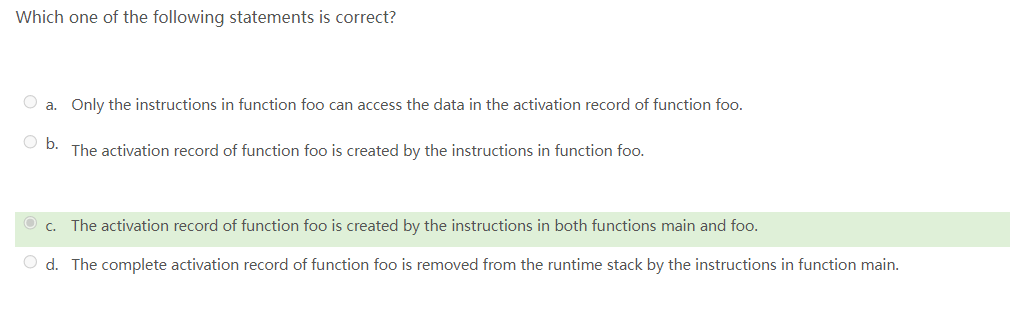

#### 函数

调用函数时内存结构

- 动态链:存入调用者的帧指针

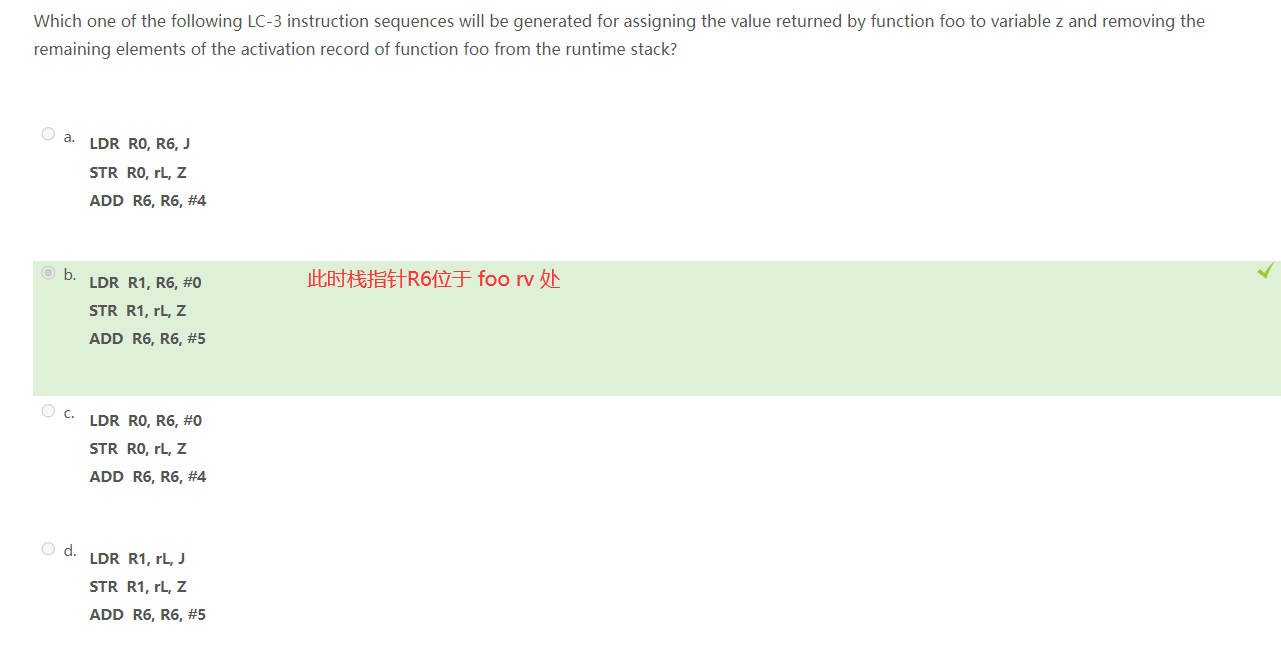

- 返回地址:调用者程序中下一指令的地址,返回时存入`R7`,使用`JSR`指令回调用者程序

- 返回值:被调用者传递给调用者的值

<img src="https://raw.githubusercontent.com/TaraTang2003/picgo-typora/main/202206141325432.png" alt="image-20220614132529359" style="zoom: 80%;" />

--作业--

<img src="https://raw.githubusercontent.com/TaraTang2003/picgo-typora/main/202206141344920.png" alt="image-20220614134435849" style="zoom:80%;" />

传递形参的指令

<img src="https://raw.githubusercontent.com/TaraTang2003/picgo-typora/main/202206141357535.png" alt="image-20220614135704471" style="zoom:80%;" /><img src="https://raw.githubusercontent.com/TaraTang2003/picgo-typora/main/202206141405697.png" alt="image-20220614140515620" style="zoom:80%;" />

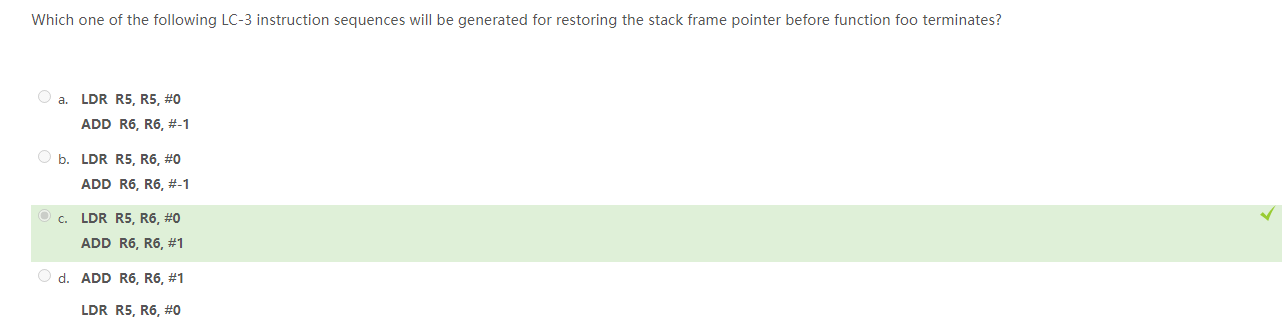

装载帧指针的指令

返回值并退出函数

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!